نگاهي دقيق به رمزورازهاي معماري Zen 2 پردازنده هاي AMD

آگنر فاگ در زمينهي ويژگيهاي زيرساختي (Low-level) و معماري نرمافزاري پردزاندهها تحقيق ميكند. آگنر همچنان درحال انتشار بهروزرسانيهاي دورهاي خود دربارهي دفترچهي راهنماي پردازندهها است كه در آن معماريهاي مختلف AMD و اينتل را مقايسه ميكند. يافتههاي او از يك ويژگي در تراشههاي Zen 2 توليدشده توسط AMD پرده برداشتهاند كه پيشاز اين درجايي بازگو نشده بودند.

آگنر براي انجام آزمايشهاي خود، فهرست بلندبالايي از بنچماركهاي ميكرو عملياتي تدارك ديده است تا تمام جزئيات عملكرد تراشهها را بيرون بكشد. نمودارهاي رسمي دورهي دستورالعمل كه توسط اينتل و AMD منتشر ميشوند، دقت كافي را ندارند و آگنر در گذشته، باگهاي فاشنشدهاي از دل پردازندههاي x86 پيدا كرد كه شامل اشكالاتي در انجام عمليات مربوط به كد AVX2 در معماري Piledriver و اشكالاتي در پايپلاين اصلي هستهي واحد مميز شناور (FPU) ميشده است.

بيشتر بخشهاي جزئيات سطح پايين يا بهعبارتي زيرساختي، براي افرادي كه چگونگي تكامل معماري Zen به Zen 2 را مطالعه كردند، آشنا است. حداكثر ميزان اندازهگيريشدهي توان عملياتي، گرفتن دستور از حافظه (Fetch) بر ترد، همچنان ۱۶ بايت است. هرچند، ناگفته نماند كه پردازنده ازانديشه متخصصين تئوري ميتواند تا حجم ۳۲ بايت دستور همراستا بر هر سيكل كلاك را (fetch/clock cycle) دريافت كند. پردازنده روي نرخ ديكود باثبات ۴ دستورالعمل بر سيكل كلاك (IPC) محدود شده است؛ اما اين ميزان ميتواند تا عدد ۶ دستورالعمل در هر سيكل افزايش يابد، فقط بهشرطي كه نيمي از دستورالعملها هركدامشان دو ميكرو عمليات توليد كنند. دراينصورت با دو دستورالعمل تك و دو دستورالعمل دوتايي روبهرو خواهيم بود. البته، درانديشه متخصصين داشته باشيد كه اين فرايند در اكثر اوقات اتفاق نميافتد.

از انديشه متخصصين تئوري، اندازهي حافظهي كش ميكرو عملياتها ۴٬۰۹۶ µops عنوان شده؛ اما ميزان مؤثر ميكرو عملياتها در يك رشته يا ترد (thread) بهتنهايي، براساس محاسبات آگنر، ۲٬۵۰۰ µops اندازهگيري شده است؛ بنابراين اين رقم در دو ترد، قاعدتا دوبرابر مؤثر خواهد شد. حلقههاي دستوري داخل حافظهي كش نيز ميتوانند با ۵ IPC (دستورالعمل بر سيكل) اجرا شوند؛ البته فراموش نكنيد كه تحت شرايط خاص گفتهشده، ممكن است ميزان IPC تا ۶ عدد نيز برسد.

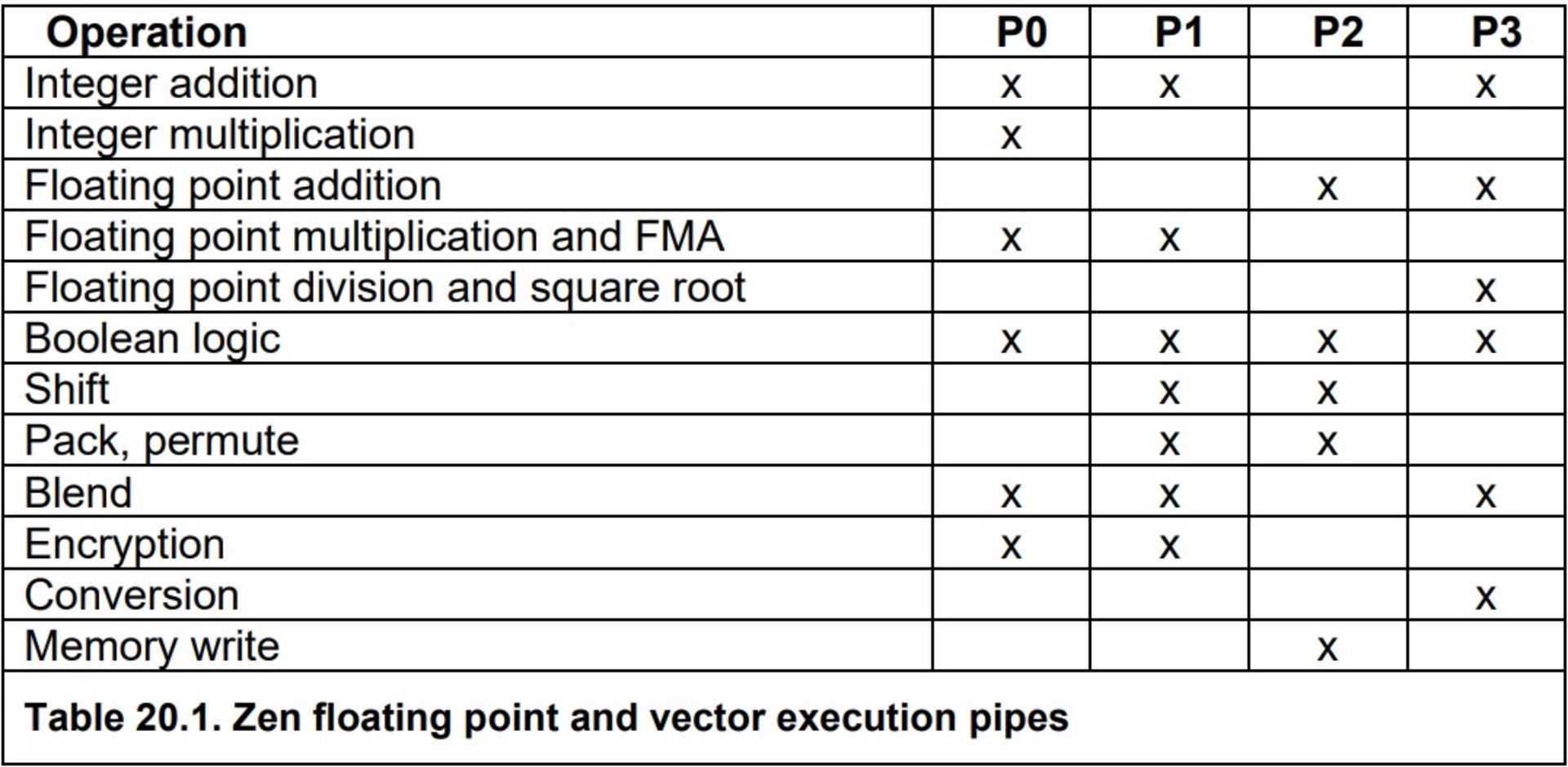

آزمايشهاي سطح پايين همچنين، برخي برتريهاي معماري Zen 2 نسبت به Zen را تأييد كردند. در معماري Zen تراشه ميتواند همزمان دو خواندن (read) داشته باشد يا توان خود را بين يك خواندن و يك نوشتن در همان سيكل تقسيم كند؛ درحاليكه در معماري Zen 2 تراشه قادر است دو خواندن و يك نوشتن را اجرا كند. براي مثال، جدول زير نشان ميدهد كه دستورالعمل مميز شناور چگونه براساس پايپهاي اجرايي مختلف باتوجهبه وظيفهي مدانديشه متخصصين (task) بهكار گرفته ميشوند.

يكي ديگر از تفاوتهايي كه AMD در Zen 2 آن را معرفي كرده، توانايي ميروركردن (mirror) حافظهي عملوندها (operand) است. اين ويژگي در برخي عملياتها ميتواند تعداد سيكل كلاكها را براي اجراي عمليات بهطرز چشمگيري، براي مثال از ۱۵ به ۲ كاهش دهد. براي اجراي موفقيتآميز عمل ميروركردن چند پيششرط لازم است كه براي مثال ميتوان بهچند مورد از آنها اشاره كرد. مورد اول اين است كه دستورالعملها بايد از رجيسترهايي همهمنظوره (عمومي) استفاده كنند، حافظهي عملوندها بايد آدرس يكساني داشته باشند، اندازهي عملوندها بايد ۳۲ يا ۶۴ بيت باشد: البته درانديشه متخصصين داشته باشيد كه بعداز نوشتن يك بستهي ۶۴ بيتي ميتوان يك بستهي ۳۲ بيتي را تحت فرايند خواندن در همان آدرس قرار داد. البته ناگفته نماند كه فرايند خواندن و نوشتن بهصورت معكوس آنچه گفته شد بههيچوجه امكانپذير نيست.

ازآنجايي كه اين ويژگي درجايي ثبت نشده است، مشخص نيست كه آيا شخصي توانسته است آن را بهصورت عملي در ارسال كد بهكار گيرد يا خير. آگنر خاطرنشان كرد كه اين قابليت بيشتر در حالت ۳۲ بيتي بهرهوري كافي خواهد داشت. وي در ادامه افزود، اگر پردازنده با استنباطهاي نادرست خاصي مواجه شود، افت عملكرد خواهد داشت. اين نارسايي را شايد بتوان علت عدم ثبت و معرفي اين قابليت دانست. AMD احتمالا قصد داشته است از تشويق توسعهدهندگان براي استفاده از اين قابليت كه احتمال ايجاد اشكال در عملكرد را بههمراه دارد، جلوگيري كند.

فاگ درنهايت انديشه متخصصين كلي خود را دربارهي Zen چنين بيان كرده است:

درنهايت ميتوان نتيجه گرفت كه ريزمعماري Zen داراي طراحي كارآمدي است و حافظهي كش و حافظهي كش ميكرو عمليات زيادي ارائه ميكند و واحدهاي اجرايي بزرگي را با توان عملياتي بسيار بالا و تأخير پايين دربر ميگيرد.

هم انديشي ها