پردازندهها چگونه طراحي و ساخته ميشوند؟ (قسمت اول)

همهي ما ميدانيم كه پردازنده يا CPU در حكم مغز يك كامپيوتر است، اما اين عبارت واقعاً به چه معني است؟ چه چيزي درون يك تراشه و در ميان ميلياردها ترانزيستور اتفاق ميافتد تا يك كامپيوتر به كار بيفتد و دستورالعملهاي پيچيده را اجرا كند؟ در اين مقاله قصد داريم به واكاوي يك CPU بپردازيم و هر آنچه از درون و بيرون باعث بهكارافتادن يك پردازنده ميشود را شرح دهيم. در اين مقالات سعي خواهيم كرد مباحثي نظير معماري كامپيوتر، اجزاي سازندهي تراشه، روش طراحي مدارهاي پردازنده، مفهوم VLSI يا تجميع در ابعاد بسيار بزرگ، ساخت فيزيكي تراشه و فناوريهاي مربوطه و خطمشي آيندهي اجراي محاسبات در كامپيوترها را پوشش دهيم.

چرخهي اجراي دستورالعمل در يك پردازنده

مباحثه خود را با روش كار يك پردازنده و كارهايي كه اين قطعهي سختافزاري قادر به انجام آن است، شروع ميكنيم و خواهيم ديد كه چگونه بلوكهاي ساختاري در يك طراحي عملياتي گرد هم ميآيند. اين بلوكهاي ساختاري شامل هستههاي پردازنده، سلسلهمراتب حافظه، پيشبينيگر انشعاب (Branch Prediction) و ديگر اجزا است.

سادهترين توضيح پيرامون روش كار يك پردازنده، همان توضيح آشنايي است كه به گوش همهي ما رسيده است. پردازنده از يك سري دستورالعمل براي انجام پارهاي از اعمال روي مجموعهاي از وروديها پيروي ميكند و نتايج خروجي را بازميگرداند. اين عمليات ممكن است شامل خواندن يك مقدار از حافظه، افزودن آن به مقداري ديگر و در نهايت بازگرداندن نتيجه به محل يا آدرس متفاوتي در حافظه باشد. محاسبه ممكن است پيچيدهتر نيز باشد؛ مثلا به كامپيوتر بگوييم اگر حاصل محاسبهي قبلي بيشتر از مقدار صفر شد، دو عدد را بر يكديگر تقسيم كن.

معماري مجموعه دستورالعمل يا ISA مفهومي در ارتباط با برنامهنويسي است و زبانهاي سطح بالا را به دستورالعملهاي قابل درك براي پردازنده تبديل ميكند

براي اينكه برنامهاي نظير يك سيستمعامل يا يك بازي در كامپيوتر اجرا شود، آن برنامه كه بهصورت مجموعهاي از دستورالعملها در حافظه قرار دارد، براي اجرا در اختيار پردازنده قرار ميگيرد. اين دستورالعملها از حافظه بارگيري شده و در سادهترين حالت ممكن، يكي پس از ديگري اجرا ميشود تا روند اجراي برنامه پايان يابد. توسعهدهندگان نرمافزار برنامههاي خود را با زبانهاي برنامهنويسي سطح بالايي نظير C++ يا پايتون مينويسند كه براي پردازنده بهصورت خام قابل درك نيست. همانطور كه ميدانيد، پردازندهها فقط زبان صفرها و يكها را متوجه ميشوند، پس بايد راهي پيدا كنيم كه دستورالعملها يا كدهاي هر برنامه و نرمافزار به چنين فرمتي تبديل شوند.

كدهاي برنامه به مجموعهاي از دستورالعملهاي سطح پايين با نام زبان اسمبلي ترجمه (كامپايل) و تبديل ميشوند كه بخشي از معماري مجموعه دستورالعمل (ISA) يا به اختصار معماري پردازنده است. اين همان مجموعه دستورالعملهايي است كه پردازنده براي درك و اجراي آن ساخته شده است. اصليترين معماريهاي مجموعه دستورالعمل يا به اختصار ISAها شامل x86، آرم، MIPS، معماري PowerPC و RISC-V ميشود. زبانهاي برنامهنويسي مختلف نحوهي نگارش و قرارگيري كلمات و عبارات و كدهاي متفاوتي دارند كه به آن سينتكس گفته ميشود؛ همانطور كه زبانهاي سطح بالايي مثل C++ و پايتون سينتكس متفاوتي دارد، ISA هم سينتكس جداگانهاي دارند.

مراحل تبديل كدهاي سطح بالاي يك برنامه به زبان ماشين

معماريهاي مجموعه دستورالعمل به دو شاخهي اصلي قابل تجزيه است؛ طول ثابت و طول متغير. معماري RISC-V از دستورالعملهايي با طول ثابت استفاده ميكند؛ يعني هر دستورالعمل تعداد بيت معين از پيش تعريفشدهاي دارد كه نوع آن دستورالعمل را تعريف ميكند. در مقابل معماري x86 از دستورالعملهايي با طول متغير استفاده ميكند. در معماري x86، امكان رمزنويسي (Encoding) دستورالعملها با روشهاي متفاوت و تعداد بيتهاي مختلف براي بخشهاي مختلف وجود دارد. به دليل وجود چنين پيچيدگي، رمزگشايي (Decoding) دستورالعمل در پردازندههاي x86 معمولاً با پيچيدهترين جزء در كل طراحي اجرايي ميشود.

دستورالعملهاي طول ثابت به دليل ساختار متداول خود امكان رمزگشايي به مراتب سادهتري دارند، اما تعداد كل دستورالعملهايي را كه يك ISA قادر به همراهي از آن است، محدود ميكند. در حالي كه نسخههاي متداول معماري RISC-V فقط چيزي در حدود ۱۰۰ دستورالعمل دارند و منبع باز هستند، معماري x86 يك دارايي فكري متعلق به اينتل است و و عدد دقيقي از تعداد دستورالعملهاي اين معماري در دسترس نيست. اين باور وجود دارد كه اين معماري از چندهزار دستورالعمل همراهي ميكند؛ اما تعداد دقيق آنها اعلام نشده است. باوجود تفاوتهايي كه در ميان معماريهاي مجموعه دستورالعمل وجود دارد، اصول زيربنايي تمامي آنها ضرورتاً يكسان است.

مثالي از دستورالعملهاي مربوط به معماري RISC-V، كدهاي عملياتي (Opcode) نگارششده در سمت راست همگي ۷ بيتي (با طول ثابت) هستند و نوع دستورالعمل را تعيين ميكند

اكنون مروري بر نحوهي اجراي يك برنامه يا مجموعهي كدهاي نوشتهشدهي آن توسط يك كامپيوتر خواهيم داشت. اجراي يك دستورالعمل در حقيقت شامل چند بخش اساسي است كه در مراحل مختلف كار يك پردازنده به بخشهاي كوچكتري تجزيه ميشوند. در ادامه اين بخشهاي كلي با زباني ساده تبيين خواهد شد.

اولين مرحله واكشي دستورالعمل (Fetch) از حافظه به پردازنده براي آغاز اجرا است. در مرحلهي دوم، دستورالعمل رمزگشايي (Decode) ميشود تا پردازنده تشخيص دهد با چه نوع دستورالعملي سر و كار دارد. انواع زيادي از دستورالعملها شامل دستورالعملهاي حسابي، دستورهاي انشعاب و دستورالعملهاي حافظه ممكن است براي اجرا در اختيار پردازنده قرار گيرد. به محض آنكه پردازنده دانست با چه نوع دستورالعملي سروكار دارد، عملوندهاي (Operand) مرتبط با دستورالعمل از حافظه يا ثباتهاي داخلي در CPU جمعآوري ميشود. براي توضيح بيشتر، اگر بخواهيم طبق دستورالعمل، عدد A و عدد B را با يكديگر جمع كنيم، تا زمانيكه مقادير دقيق عملوندهاي A و B مشخص نباشد، انجام عمل جمع ناممكن است. پس از آنكه پردازنده عملوندها را براي جايگذاري در دستورالعمل فراخواند، وارد مرحلهي اجراي دستورالعمل ميشود كه در آن عملياتي روي مقادير ورودي اين عمليات ميتواند جمع اعداد ورودي، انجام يك عمليات دستكاري منطقي روي اعداد يا عبور دادن اعداد بدون اصلاح آنها باشد. پس از محاسبهي نتيجه ممكن است نياز به دسترسي به حافظه براي ذخيرهي مقدار نتيجه باشد يا ممكن است پردازنده نتيجه را فقط در يكي از ثباتهاي داخلي خود نگه دارد. پس از ذخيرهسازي نتيجه، پردازنده وضعيت المانهاي مختلف را بهروزرساني ميكند و آمادهي اجراي دستورالعمل بعدي ميشود.

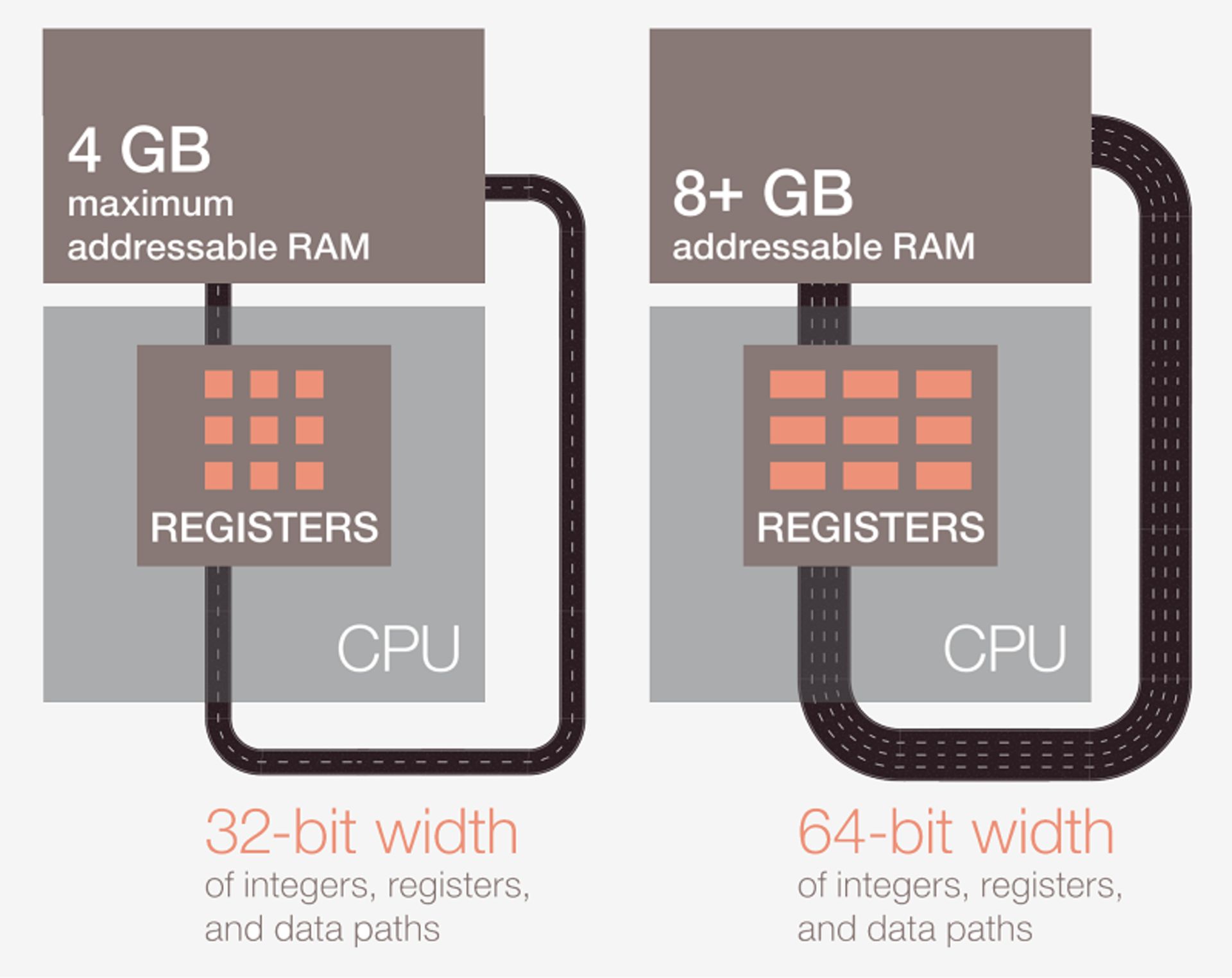

بيشتر پردازندههاي مدرن ۶۴ بيتي هستند؛ يعني مقادير دادهها را با پهناي باند ۶۴ بيتي از آدرسهاي حافظه و ثباتها فرا ميخوانند و مورد پردازش قرار ميدهند و نتايج پردازش را به آدرسهاي حافظه باز ميگردانند. بنابراين يك معماري پردازنده ۶۴ بيتي در مقايسه با يك مدل ۳۲ بيتي امكان فراخواني و پردازش دو برابر داده را در آن واحد دارد.

توضيحاتي كه در در مورد نحوهي عملكرد يك پردازنده ارائه شد، بسيار خلاصه و سادهسازي شده بود. بيشتر پردازندههاي مدرن مراحل معدود يادشده را براي افزايش بازدهي به دستكم ۲۰ مرحلهي خردتر تقسيم ميكنند. به عبارت ديگر، هر چند يك پردازنده در هر چرخهي كاري يا سيكل كلاك اجراي چندين دستورالعمل را شروع ميكند، ادامه ميدهد و به سرانجام ميرساند؛ اما براي اجراي هر دستورالعمل از آغاز تا اتمام، ممكن است ۲۰ سيكل كلاك يا حتي بيشتر لازم باشد. به چنين مدلي در اصطلاح يك پايپلاين اطلاق ميشود. پر شدن يك خط لوله با سيال در جريان مدتي به طول مي انجامد، اما پس از آن يك خروجي پايدار و ثابت از آن سيال به دست ميآيد. در پايپلاين پردازنده، بهجاي سيال دستورالعملها به جريان ميافتند.

چرخهي كامل اجراي يك دستورالعمل فرايندي پيچيده و محاسبهشده است، اما اين بهمعناي اجراي همزمان تمامي دستورالعملها نيست. براي مثال عمل جمع با سرعت بسيار زياد اجرا ميشود؛ اما عملياتهايي مثل تقسيم يا بارگذاري از حافظه ممكن است صدها سيكل كلاك به طول بيانجامد. بهجاي معطلكردن كل ساختار پردازنده براي اتمام يك دستورالعمل كنداجرا، بيشتر پردازندههاي مدرن به نحوي بدون پيروي از نظم و ترتيب خاص كار ميكنند. به عبارت ديگر پردازنده تعيين ميكند كه اجراي چه دستورالعملي در زماني معين بيشترين سودمندي را دارد و در عين حال ساير دستورالعملهايي را كه هنوز آماده اجرا نيست، بافر ميكند. اگر دستورالعمل جاري هنوز آمادهي اجرا نباشد، پردازنده در خطوط كد به جلو پرش ميكند و بهدنبال به بخشي از دستورالعمل كه آمادهي اجرا است ميگردد.

دستورالعملها بهمانند سيالي در پايپلاين پردازنده به جريان ميافتد و در هر مرحله از پايپلاين، پردازش دستورالعملهاي متعددي در جريان است

برخي از پردازندههاي مدرن امروزي، علاوه بر اجراي نامنظم دستورالعملها، روشي با نام معماري سوپراسكالر را به كار ميبندند. با اين روش در هر زمان معين، پردازنده در حال اجراي دستورالعملهاي بسياري در يك مرحلهي خاص از پايپلاين (مثل مرحلهي واكشي، رمزگشايي، اجرا و ذخيرهسازي) است. در عين حال ممكن است پردازنده منتظر صدها دستورالعمل ديگر براي آغاز اجرا باشد.

در شكل فوق، هر مربع رنگي نشاندهندهي يك دستورالعمل (كد) در پايپلاين، در انتظار ورود به آن يا اجراشده و خارجشده از پايپلاين است. در هر مرحله از پايپلاين كدهاي متفاوتي در حال پردازش بوده و در عين حال ممكن است دستورالعملهاي زيادي در بافر منتظر ورود به پايپ لاين باشند.

در اينجا بهتر است با مفهوم IPC كه تأثير بهسزايي در سطح عملكرد يك پردازنده دارد، آشنا شويم. IPC مخفف عبارت Instruction per Clock است كه مفهوم آن ميانگين تعداد دستورالعملهاي اجراپذير در هستههاي پردازنده در هر سيكل كلاك است. محاسبهي IPC در يك ماشين كار نسبتا پيچيدهاي است. براي انجام اين كار مجموعهاي بهخصوص از كدها براي اجرا به ماشين داده ميشود و تعداد دستورالعملهاي سطح ماشين براي تكميل اجراي آن كدها محاسبه ميشود. در گام بعد، با استفاده از زمانسنجهاي سطح بالا تعداد سيكلهاي كلاك موردنياز براي كاملكردن آن تعداد دستورالعمل روي سختافزار واقعي اندازهگيري ميشود. با تقسيم تعداد دستورالعملها بر تعداد سيكلهاي كلاك اندازهگيريشده، رقم IPC ماشين مورد انديشه متخصصين محاسبه ميشود. با ضرب IPC اندازهگيريشده در سرعت كلاك (بر حسب هرتز) و تعداد هستههاي پردازنده، تعداد دستورالعمل اجراشدني در هر ثانيه يا تعداد عملياتهاي مميز شناوري محاسبه ميشود كه در هر ثانيه بهوسيلهي پردازندهي مدانديشه متخصصين اجراشدني است. در نهايت، تعداد دستورالعملهاي اجراشدني بهوسيلهي پردازنده در هر ثانيه كه با واحد گيگافلاپس يا ميليارد عمل اعشاري در ثانيه بيان ميشود، معياري از سطح عملكرد پردازندهي مدانديشه متخصصين است.

تعداد دستورالعملهاي اجراپذير در هر سيكل كلاك براي پردازنده عدد ثابتي نيست و بستگي به نحوهي تعامل و برهمكنش نرمافزار و برنامهي در حال اجرا با بخش سختافزاري سيستم دارد. با وجود اين، طراحان تراشه سعي ميكنند، با تكيه بر روشهايي مانند استفاده از چندين واحد محاسبهگر منطقي (ALU) در هر هسته و پايپلاينهاي دستورالعمل كوتاهتر، عدد IPC را در مقايسه با مقدار متوسط آن افزايش دهند.

مجموعه دستورالعملها (Instruction Set) نيز بر عدد IPC پردازنده تأثيرگذار است. هرچه مجموعه دستورالعملها سادهتر باشد، IPC پردازنده افزايش مييابد و هرچه با دستورالعملهاي پيچيدهتري روبهرو باشيم، بالتبع IPC كاهش پيدا ميكند. بنابراين، IPC پردازنده براي اجراي محاسبات مميز شناور با دقت واحد (FP32) در مقايسه با اجراي محاسبات با دقت مضاعف (FP64) عدد بزرگتري است. آنچه ميزان كارايي پردازنده را مشخص ميكند، تركيبي از IPC و سرعت كلاك و تعداد هستهها است. با اين حال، سازندگان پردازنده عموما عدد IPC را در مشخصات رسمي آن ذكر نميكنند.

براي آنكه پردازنده بهطور همزمان قادر به اجراي دستورالعملهاي زيادي باشد، ممكن است كپيهاي زيادي از هر مرحله پايپلاين ايجاد كند. اگر پردازنده بداند كه دو دستورالعمل بهطور هم زمان آمادهي اجرا است و وابستگي بين آنها وجود ندارد و نيازي به اتمام يكي و آغاز ديگري نيست، هر دو دستورالعمل را در يك زمان به اجرا در ميآورد. يكي از راههاي پيادهسازي اين راهكار، پردازش چندرشتهاي همزمان (Simultaneous Multithreading ) يا SMT است. پردازندههاي اينتل و AMD در حال حاضر از شيوهي SMT دوخطي استفاده ميكنند. در اين پردازندهها هر هستهي فيزيكي به دو هسته مجازي تقسيمبندي شده و هر هستهي بهدستآمده يك ترد يا رشته نامگذاري ميشود. بدين ترتيب هر هسته امكان اجراي دو جريان يا دو رشته دستورالعمل را بهطور همزمان خواهد داشت. IBM در حال توسعهي پردازندههايي با قابليت اجراي SMT هشت خطي است.

مولتي تردينگ يا پردازش همزمان چند رشته در هر هسته، باعث كاهش چشمگير زمان اجراي دستورالعمل ميشود

براي اجراي حسابشدهي چنين فرايندي، يك پردازنده علاوه بر هستههاي اصلي از اجزاي اضافي زيادي برخوردار است. صدها ماژول مجزا در يك پردازنده وجود دارد كه هر يك هدف خاصي را برآورده ميكنند. در اين مقاله به جهت پرهيز از اطالهي كلام تنها به مطالعه دو قسمت اصلي حافظه كش و پيشبينيگر انشعاب بسنده خواهيم كرد. اجزاي ديگري نظير بافرهاي بازآرايي، Register Alias Table و ايستگاههاي رزرواسيون وجود دارد كه در اين مقاله از توضيح آنها صرفانديشه متخصصين ميشود.

مفهوم حافظهي كش ممكن است كمي گيجكننده باشد، چرا كه آنها درست مثل رمِ سيستم يا درايو SSD دادهها را در خود ذخيره ميكنند؛ اما آنچه باعث تمايز حافظهي كش از قطعات مشابه خود ميشود، سرعت بسيار بالاتر و تأخير كمتر در دسترسي به دادهها است. هر چند حافظهي رم سيستم بسيار سريع است، سرعت آن براي همگامشدن با فرآيندهاي اجراي دستورالعمل پردازنده همچنان بسيار نارسا است. تأمين دادههاي مورد نياز پردازنده از سوي حافظهي رم ممكن است صدها سيكل كلاك به طول بيانجامد و امكان تغذيهي بههنگام پردازندهاي كه تنها در يك سيكل كلاك چندين دستورالعمل را اجرا ميكند، با چنين سرعتي وجود ندارد. حالا اگر دادهها هنوز روي حافظهي رم قرار نگرفته باشد، دسترسي به دادههاي مورد نياز در حافظه SSD دهها هزار سيكل كلاك به طول ميانجامد. بدون وجود حافظههاي به مراتب سريعتر كش، پردازنده از كار باز خواهد ماند.

سلسله مراتب و ميزان تأخير در دسترسي پردازنده به اجزاي مختلف حافظه در سيستم

پردازندهها بهطور معمول ۳ سطح از حافظهي كش را در خود دارند كه بخشي از ساختاري با نام سلسلهمراتب حافظه را شكل ميدهد. كش سطح ۱ (L1) كوچكترين و سريعترين حافظهي كش موجود در تراشه است، كش سطح ۲ (L2) از اين انديشه متخصصين وضعيت متعادلي دارد و سومين سطح از حافظهي كش (L3) كندترين و بيشترين بخش حافظهي كش را به خود اختصاص ميدهد. در سلسله مراتب حافظهي يك پردازنده، ثباتهاي كوچك يك مرحله بالاتر از حافظهي كش قرار دارد كه در خلال محاسبه يك مقدار دادهي واحد (۱ بيت) را به خود ميگيرد. اين ثباتها سريعترين تجهيزات ذخيرهسازي در يك سيستم كامپيوتري هستند كه سرعت آنها چندينبرابر اجزاي ديگر است. زمانيكه كامپايلر برنامه سطح بالا را به زبان اسمبلي ترجمه ميكند، بهترين راه بهكارگيري اين ثباتها را نيز تعيين ميكند.

زمانيكه پردازنده دادهها را از حافظه فراميخواند، ابتدا مطالعه ميكند آيا دادههاي مورد انديشه متخصصين در حال حاضر در كش سطح ۱ قرار گرفته يا خير. اگر دادههاي مورد انديشه متخصصين در اين كش قرار گرفته باشد، به سرعت و ظرف يكي دو سيكل كلاك در اختيار پردازنده قرار ميگيرند. اگر دادهها در كش L1 قرار نگرفته باشند، پردازنده همين روال را در مورد كش سطح ۲ و سپس كش سطح ۳ پيگيري ميكند. قطعات حافظهي كش به نحوي پيادهسازي ميشود كه محتواي آن براي هسته كاملاً شفاف باشد. هسته تنها دادهها را در آدرس مشخصي از حافظه درخواست ميكند و هر سطحي از حافظهي كش كه در سلسله مراتب، دادههاي مورد انديشه متخصصين را در خود ذخيره داشته باشد بهسرعت پاسخ پردازنده را خواهد داد. با حركت به سمت مراحل بعدي در سلسله مراتب حافظه، اندازه و ميزان تأخير حافظه عموماً تا چندين برابر افزايش مييابد. در آخر اگر پردازنده نتواند دادهها را در يكي از سطوح كش بيابد، به ناچار و با واسطهي جزيي از پردازنده با نام كنترلر حافظه، به حافظه اصلي (رم) مراجعه خواهد كرد.

در يك پردازندهي معمولي، هر هسته از دو جزء حافظه كش سطح يك برخوردار است؛ يكي از آنها براي ذخيرهي داده و ديگري براي ذخيرهي دستورالعملها استفاده ميشود. ظرفيت كش سطح يك در مجموع حدود ۱۰۰ كيلوبايت است و اندازهي آن بسته به نوع تراشه، نسل و فناوري ساخت متغير است. معمولاً هر هسته با يك كش سطح ۲ اختصاصي همراه ميشود؛ گرچه گاه اين قطعه از حافظه كش بين دو هسته به اشتراك گذارده ميشود. ظرفيت كش سطح دو معمولاً از چند صد كيلو بايت تجاوز نميكند. در نهايت كش سطح ۳ بين تمام هستهها به اشتراك گذارده ميشود و ظرفيتي معادل چند ده مگابايت دارد.

نحوهي توزيع حافظهي كش در بين هستههاي پردازندهاي با معماري ذن AMD

وقتي يك پردازنده در حال اجراي يك قطعه كد است، دستورالعملها و مقادير دادهاي كه به آن نياز است، در حافظهي كش ذخيرهسازي شده يا به اصطلاح كش ميشود. با اين شيوه سرعت اجرا بهطور چشمگيري افزايش مي يابد؛ چرا كه پردازنده براي دستيابي به دادههاي مورد نياز خود نيازي به تعامل دائمي با حافظهي اصلي ندارد. در مورد نحوهي قرارگيري حافظهي اصلي و SSD در زير لايههاي بعدي سلسلهمراتب حافظه، در ادامه بيشتر صحبت خواهيم كرد.

گذشته از حافظهي كش، يكي از بلوكهاي ساختاري كليدي هر پردازندهي مدرن بخشي است كه پيشبينيگر انشعاب خوانده ميشود. دستورالعملهاي انشعاب شبيه به گزارهي «اگر» براي يك پردازنده است. اگر شرايطي برقرار باشد (If True)، يك مجموعه از دستورالعملها اجرا ميشود و اگر آن شرايط برقرار نباشد (If False)، مجموعه دستورالعمل ديگري به اجرا گذارده ميشود. براي مثال دو مقدار عددي با يكديگر مقايسه ميشود و اگر آن دو مقدار برابر باشد، عمليات معيني اجرا ميشود. حال اگر اين دو مقدار نابرابر باشد، بايستي عمليات ديگري اجرا شود. چنين دستورالعملهاي انشعابي بهشدت در پايپلاين رايج بوده و ممكن است حداكثر ۲۰ درصد تمامي دستورالعملها را دربرگيرد.

اين دستورالعملهاي انشعاب در ظاهر ممكن است چندان مسئلهي مهمي به انديشه متخصصين نرسد، اما در عمل چالشي بر سر راه عملكرد درست يك پردازنده است. از آنجايي كه پردازنده در هر مقطع زماني ممكن است در حال اجراي ۱۰ يا ۲۰ دستورالعمل بهطور همزمان باشد، دانستن اينكه چه دستورالعملهايي بايد به اجرا درآيد، حائز اهميت است. پنج سيكل كلاك براي شناسايي يك دستورالعمل انشعاب لازم است و ده سيكل كلاك ديگر بايد طي شود تا مشخص گردد، آيا شرايط مورد انديشه متخصصين انشعاب برقرار هست يا نيست. در اين بازهي زماني، پردازنده ممكن است پردازش دهها دستورالعمل اضافي را بدون آنكه حتي بداند دستورالعملهاي درستي (از انديشه متخصصين سازگاري با انشعاب) براي اجرا انتخاب شدهاند، آغاز كند.

براي غلبه بر اين اشكال، تمامي پردازندههاي ردهبالا از تكنيكي با نام Speculation استفاده ميكنند. با اين شيوه پردازنده با برخورداري از واحدي به نام پيشبينيگر انشعاب دستورالعملهاي انشعاب را تعقيب ميكند و حدس ميزند كه آيا انشعاب معين اختيار خواهد شد يا خير. اگر اين پيشبيني درست از آب در بيايد، پردازنده از قبل، اجراي دستورالعملهاي پسآيند سازگاري را آغاز ميكند و عملكرد تسريع ميشود و بهبود مييابد. اما اگر پيشبيني نادرست باشد، پردازنده روند اجرا را متوقف ميكند، تمامي دستورالعملهاي نادرستي كه اجراي آنها آغاز شده حذف ميشود و مراحل اجرا از آخرين نقطهي درست، از سر گرفته ميشود.

طرح كلي معماري هستهي Zen 2 و جايگاه پيشبينيگر انشعاب (بلوك سبزرنگ) در آن

پيشبينيگرهاي انشعاب به نوعي پايهايترين اشكال يادگيري ماشين هستند؛ چرا كه پيشبينيگر رفتار انشعابها را با جريان يافتن دستورالعملها در آن پيشبيني ميكند. اگر پيشبينيگر به دفعات زياد پيشبيني غلط انجام دهد، بهزودي رويكرد درست را خواهد آموخت. دههها تحقيق در مورد فنون پيشبيني انشعاب سبب شده است كه در پردازندههاي مدرن امروزي، در بيش از ۹۰ درصد موارد پيشبينيهاي درستي انجام شود. تكنيك Speculation پردازنده را قادر به اجراي دستورالعملهايي ميكند كه بهجاي قرار گرفتن در صفوف شلوغ داده، از قبل آمادهي پردازش است؛ در عين حال پردازنده را در معرض آسيبهاي امنيتي نيز قرار ميدهد. حفرهي امنيتي مشهور Spectre حملات خود را از راه پيشبينيگر انشعاب و با نفوذي مبتني بر Speculation تحميل ميكند. بنابراين برخي از جنبههاي اين تكنيك بايد بازبيني و بازطراحي شود تا از نفوذ دستورالعملهاي غير ايمن در پايپلاين و نشتي اطلاعات حافظه جلوگيري به عمل آيد؛ حتي اگر تأثير كوچكي بر سطح عملكرد بگذارد.

معماريهاي مورد استفاده در پردازندههاي مدرن، راهي دراز و پرفرازونشيب در خلال دهههاي گذشته پيموده است. ابداعات و طراحيهاي هوشمندانه منجر به بهبود عملكرد و بهكارگيري بهتر اجزاي ناپيداي سختافزاري ميشود. تراشهسازان در مورد جزئيات فناوريهاي بهكاررفته در روند ساخت پردازنده بسيار رمزآلود عمل ميكنند و دانستن آنچه كه دقيقاً درون يك پردازنده و در خلال اجراي دستورالعملها اتفاق ميافتد، ناممكن است. با وجود اين اصول كار پردازندههاي كامپيوتر و استانداردهايي كه در روند اجراي محاسبات در پردازندهها رعايت ميشود، نسبتا مشخص است. ممكن است اينتل دست به اقدامي مخفيانه براي بهبود عملكرد حافظهي كش خود بزند يا AMD از يك واحد پيشبينيگر انشعاب پيشرفته با كارايي بهتر استفاده كند، اما در مجموع هر دو دست به اقدامات مشابهي ميزنند.

آشنايي با عناصر سازنده و اجزاي يك پردازنده

اكنون كه با روش كار پردازندهها آشنا شديم، وقت آن است كه وارد لايههاي عميقتر پردازنده شويم و با اجزا و بخشهاي داخلي آن آشنايي بيشتري پيدا كنيم. همانطور كه احتمالا ميدانيد، پردازندهها و ديگر مدارات ديجيتالي مجتمع از اجزايي با نام ترانزيستور ساخته شدهاند. ساده ترين راه براي داشتن دركي از يك ترانزيستور تصور سوئيچي با سه پايه يا پين است. گيت منطقي وسيلهاي الكترونيكي مركب از يك يا چند ترانزيستور است كه عمليات منطقي را روي دادههاي باينري (مركب از ۰ و ۱) انجام ميدهد. زمانيكه گيت باز باشد، امكان عبور جريان الكتريسيته از درون ترانزيستور وجود دارد و با بستهشدن گيت، جرياني عبور نخواهد كرد. ترانزيستور درست بهمانند كليد برق روي ديوار عمل ميكند، اما بسيار كوچك تر و بسيار سريعتر است و توانايي كنترل جريان را نيز دارد.

در پردازندههاي مدرن دو نوع ترانزيستور اصلي به كار ميرود: نوع pMOS و نوع nMOS كه به اختصار به آن انواع p و n نيز گفته ميشود. ترانزيستور nMOS با شارژ شدن گيت يا تنظيم حالت High، امكان عبور جريان را فراهم ميكند و ترانزيستور pMOS جريان را در صورتي عبور ميدهد كه گيت دشارژ شده يا روي حالت low تنظيم شود. با تركيب اين دو نوع ترانزيستور به طوري كه يكي مكمل ديگري باشد، امكان ساخت گيتهاي منطقي CMOS وجود دارد. در اين قسمت از مقاله قصد نداريم وارد جزئيات متخصص و ظريف نحوهي كار ترانزيستورها شويم.

گيت منطقي يك وسيلهي ساده است كه ورودي را دريافت كرده، عملياتي را روي آن اجرا ميكند و نتيجه را بهعنوان خروجي به دست ميدهد. براي مثال يك گيت AND خروجي خود را اگر و تنها اگر همه وروديهاي گيت روشن باشد، روشن خواهد كرد. يك گيت NOT يا وارونگر (Inverter) خروجي خود را در صورتي روشن ميكند كه ورودي خاموش باشد. با تركيب اين دو گيت، يك گيت NAND يا NOT-AND تشكيل ميشود كه اگر و تنها اگر هيچ يك از وروديها روشن نباشند، خروجي خود را روشن ميكند؛ البته گيتهاي ديگري نظير XOR ،NOR ،OR و XNOR نيز در مدارهاي منطقي يافت ميشود. در ادامه خواهيم ديد كه چگونه دو نوع گيت اساسي منطقي وارونگر و NAND با استفاده از ترانزيستورها طراحي ميشود.

گيتهاي منطقي NAND و وارونگر تركيبي از سيگنالهاي ورودي، خروجي، ترانزيستورها و البته اتصال زمين است

در گيت وارونگر، يك ترانزيستور نوع pMOS در بالاي گيت قرار ميگيرد كه به خطوط حامل توان متصل است و يك ترانزيستور nMOS در پايين گيت نقش اتصال زمين را بازي ميكند. ترانزيستورهاي pMOS را روي نقشه مدار با دايرهي كوچكي كه به گيت خود متصل است، نشان داده شده و ترانزيستورهاي nMOS تنها به شكل يك پارهخط كوچك عمودي بيان ميشود. از آن رو كه ترانزيستورهاي pMOS با خاموش بودن ورودي، جريان را عبور ميدهند و ترانزيستورهاي nMOS در صورت شارژ ورودي اقدام به هدايت جريان ميكنند، ميتوان دريافت كه سيگنال در Out (خروجي) گيت همواره مخالف سيگنال در In (ورودي) است.

در گيت NAND چهار ترانزيستور مختلف وجود دارد و امكان تغذيه با دو ورودي فراهم است. مادامي كه دستكم يكي از وروديها خاموش باشد، خروجي گيت روشن است. اتصال ترانزيستورها در قالب شبكههاي ساده نظير گيتهاي يادشده، همان فرآيندي است كه براي طراحي گيتهاي منطقي بسيار پيچيده و مدارات تعبيهشده در يك پردازنده، مورد استفادهي مهندسان تراشهساز قرار ميگيرد.

با بلوكهاي ساختاري بهسادگي گيتهاي منطقي، داشتن دركي از نحوهي تركيب و تبديل آنها به يك تراشه محاسبهگر پيشرفته شايد سخت به انديشه متخصصين برسد. فرايند طراحي چنين تراشههايي در برگيرندهي تركيب گيتهاي متعدد براي ساخت مداري كوچك است كه توانايي انجام يك عمل محاسباتي ساده را دارد. پس از آن تعداد زيادي از اين مدارهاي كوچك تركيب ميشود تا ساختاري براي انجام يك عمل پيچيدهتر به دست آيد. فرايند تركيب اجزاي جداگانهي سادهتر نظير انواع گيتهاي منطقي و تركيب آنها براي دستيابي به يك طراحي عملياتي و در نهايت مدار مجتمعي كه قادر به اجراي محاسبات پيچيده با سرعت بسيار بالايي باشد، دقيقا همان شيوهاي است كه امروزه در ساخت پردازندههاي مدرن متخصصد دارد. يك تراشهي امروزي ساختاري مركب از مدارهاي منطقي بيشمار است كه ميلياردها ترانزيستور را در خود جاي ميدهد.

در اينجا يك مثال ساده باعث درك بهتري از مباحثه ميشود. ميخواهيم روش كار مدار جمعكنندهي يكبيتي را مرور كنيم. اين مدار ۳ مقدار ورودي را دريافت ميكند كه شامل مقدار A، مقدار B و سيگنال Carry-In است و دو خروجي شامل مقدار Sum و سيگنال Carry-Out به دست ميدهد. در طراحي مبنا از ۵ گيت منطقي استفاده ميشود. اين گيتها با يكديگر لينك ميشوند تا جمعكنندهاي با هر اندازهي دلخواه بسازند. در طراحيهاي مدرن پردازنده، اگرچه اين فرايند با بهينهسازي برخي از مدارهاي منطقي و سيگنالهاي حامل داده، پيشرفتهاي زيادي به خود ديده؛ اما اصول كار همچنان يكسان است.

طرحي از يك مدار منطقي جمعكنندهي يك بيتي

خروجي Sum در صورتي روشن ميشود كه يكي از مقادير A يا B و نه هر دو روشن باشد يا سيگنال Carry-In وجود داشته و مقادير A و B هر دو روشن يا هر دو خاموش باشد. سيگنال Carry-Out كمي پيچيدهتر است. اين سيگنال وقتي فعال ميشود كه A و B هر دو در يك زمان روشن شود يا سيگنال Carry-In موجود باشد و يكي از دو مقدار A يا B روشن باشد. براي اتصال چند جمعكنندهي يك بيتي براي ساخت يك جمعكننده با پهناي بيشتر، فقط بايد سيگنال Carry-Out بيت قبلي را به سيگنال Carry-In بيت جاري متصل كرد. هرچه مدارها پيچيدهتر باشد، ازدحام گيتهاي كوچك منطقي بيشتر ميشود؛ اما آنچه گفته شد، سادهترين راه براي جمعبستن دو عدد است. در پردازندههاي مدرن از مدارهاي جمعكنندهي پيچيدهتري استفاده ميشود و مطالعه چنين مدارهايي از حوصلهي اين مقاله خارج است. پردازندهها علاوه بر مدارهاي جمعكننده، دربرگيرندهي واحدهايي براي انجام عمل تقسيم، ضرب و نسخههاي اعشاري تمامي اين اعمال حسابي است.

تركيب رشتهاي از گيتها مشابه آنچه گفته شد، براي انجام پارهاي از عملياتها روي مقادير ورودي با نام منطق تركيبي شناخته ميشود. با اين حال، اين نوع منطق تنها شيوهي شناختهشده در دنياي كامپيوترها نيست. اگر نتوان دادهها را ذخيره كرده يا وضعيت هر پارامتري را رديابي كرد، استفاده از اين شيوه چندان راهگشا نخواهد بود. براي اينكه امكان ذخيرهسازي دادهها وجود داشته باشد، از منطق ترتيبي استفاده ميشود. منطق ترتيبي با اتصال دقيق وارونگرها و ساير گيتهاي منطقي به نحوي انجام ميپذيرد كه خروجيهاي هر گيت بازخوردي به ورودي آنها ارائه دهد. از اين حلقههاي بازخورد براي ذخيره كردن يك بيت داده استفاده ميشود و با نام رم استاتيك يا SRAM شناخته ميشوند. عبارت رم استاتيك در مقابل رم ديناميك در حافظههاي DRAM قرار ميگيرد؛ چرا كه در نوع استاتيك، دادههاي در حال ذخيره همواره بهطور مستقيم به ولتاژ مثبت يا زمين متصل هستند.

روش استاندارد براي پيادهسازي يك بيت واحد SRAM استفاده از ۶ ترانزيستوري است كه در شكل زير ترسيم شده است. سيگنال بالايي WL كه مخفف عبارت Word Line است، آدرس بوده و زمانيكه اعمال شود، دادهي ذخيرهشده در اين سلول يك بيتي به Bit Line كه با حرف BL مشخص شده، ارسال ميشود. خروجي BLB يا Bit Line Bar درست مقدار وارونشدهي Bit Line است. دو نوع ترانزيستور را در اين مدار ميتوان شناسايي كرد و دريافت كه ترانزيستورهاي M3 و M1 و در سوي ديگر M4 و M2 تشكيل يك گيت وارونگر را دادهاند.

طرحي از يك مدار منطقي SRAM براي ذخيرهسازي يك بيت داده

SRAM همان عنصري است كه از آن براي ساخت حافظههاي كش فوق سريع و ثباتهاي درون پردازنده استفاده ميشود. اين عنصر اگرچه بسيار پايدار است، اما براي نگهداري يك بيت داده نياز به ۶ تا ۸ ترانزيستور دارد؛ بنابراين ساخت چنين مداري از انديشه متخصصينات هزينه، پيچيدگي و فضاي موجود در تراشه در مقايسه با DRAM بسيار گران تمام ميشود. حافظههاي رم ديناميك، در نقطهي مقابل، بهجاي استفاده از گيتهاي منطقي و ترانزيستورها براي ذخيرهي داده، از خازنهاي بسيار ريز استفاده ميكنند؛ اين حافظهها را ديناميك ميناميم چرا كه خازن مستقيم به جريان برق يا زمين متصل نيست و امكان تغيير ولتاژ آن بهصورت ديناميك وجود دارد. در اين حافظهها تنها يك ترانزيستور واحد وجود دارد كه از آن براي دسترسي به دادهي ذخيرهشده در خازن استفاده ميشود.

مدار حافظهي DRAM شامل يك ترانزيستور و يك خازن براي ذخيرهسازي يك بيت داده

از آنجايي كه حافظهي DRAM به ازاي هر بيت داده تنها به يك ترانزيستور واحد نياز دارد و طراحي آن بسيار مقياسپذير است، امكان ساخت حافظههاي بسيار چگال و ارزانارزش از اين نوع وجود دارد. يكي از اشكالات رم ديناميك اين است كه ظرفيت شارژ خازن آنقدر كم است كه بهطور دائم بايد از نو شارژ شود. به همين دليل است كه وقتي كامپيوتر خود را خاموش ميكنيد، تمامي خازنها تخليه ميشود و هر آنچه در اين حافظه بارگذاري شده، از دست ميرود. تركيبي از مدارهاي كوچك شكل فوق در سطر و ستونهاي پرشمار ساختار حافظهي DRAM سيستم را شكل ميدهد.

شركتهايي مثل اينتل، AMD و انويديا طرحي دقيق از نحوهي كار پردازندههاي خود ارائه نميكنند، بنابراين نمايش دياگرامي كامل از مدارهاي منطقي يك پردازندهي مدرن ناممكن است؛ با وجود اين، مثالي كه از يك مدار جمعكنندهي ساده زده شد، ميتواند تصور مناسبي از نحوهي كار يك پردازنده و چگونگي تجزيهي آن به گيتهاي منطقي، عناصر ذخيرهسازي و در نهايت ترانزيستورها ايجاد كند.

اكنون كه با روش كار و طرز ساخت بعضي از اجزاي اساسي پردازندهها آشنا شديم، بايد دريابيم كه چگونه همهي اجزا به يكديگر متصل و با يكديگر همگام ميشوند. همه اجزاي كليدي يك پردازنده به عاملي با نام سيگنال كلاك متصل ميشوند. اين سيگنال در بازههاي از پيش تعريفشده با نام فركانس، بين دو حد بالا و پايين نوسان ميكند. سيگنال كلاك توسط قطعهاي با نام مولد سيگنال (Signal Generator) كه يك نوسانساز الكترونيكي است، توليد ميشود. نوسانساز متشكل از برد مدارات پيزوالكتريك از جنس كوارتز يا سراميك است. اين مولد، سيگنالي با زمانبندي دقيق براي همگامسازي عملكرد مدارهاي منطقي مختلف درون تراشه توليد ميكند. مولد سيگنال سينوسي را در ورودي دريافت كرده و طي مراحلي آن را تبديل به يك موج مربعي سادهي متقارن يا موج پيچيدهتري ميكند و تحويل تراشه ميدهد.

سيگنال كلاك ايدهآل يك پردازندهي كامپيوتري كه به شكل يك موج مربعي تكرار شونده بين دو مقدار (ولتاژ) بالا و پايين است

اجزاي منطقي پردازنده همگام با اوج و فرود سيگنال دريافتي، مقادير را تبديل و جايگزين (سوييچ) كرده و محاسبات را اجرا ميكنند. با همگامكردن تمامي اجزا با يكديگر ميتوان اطمينان يافت كه دادهها همواره با زمانبندي مناسبي تحويل و دريافت ميشود، بهطوريكه هيچ خللي در كار پردازنده پديد نميآيد.

خوانندگان اين مقاله ممكن است با مفهوم اوركلاكينگ آشنا باشند كه در آن كلاك پردازنده بهطور دستي يا از طريق متدهاي نرمافزاري افزايش مييابد تا سطح عملكرد تراشه بهبود يابد. اين بهبود سطح عملكرد ناشي از تسريع فرايند سوئيچ ترانزيستورها و مدارهاي منطقي با سرعتي بيشتر از آن چيزي است كه در طراحي پيشبيني شده است. از آنجايي كه در هر ثانيه سيكلهاي كلاك بيشتري پيموده ميشود، كار بيشتري قابل انجام است و پردازنده كارايي بالاتري دارد؛ هرچند اين افزايش سطح عملكرد نقطهي بيشينهاي دارد. فركانس يا سرعت كلاك پردازندههاي مدرن عددي بين ۳ تا ۴/۵ گيگاهرتز است و در طول يك دهه گذشته اين رقم تغيير چنداني به خود نديده است. درست همچون يك زنجير فلزي كه استحكام آن برابر با استحكام ضعيفترين حلقه است، حداكثر سرعت كلاك عملياتي يك پردازنده را كندترين بخش آن مشخص ميكند. هر جزء واحد پردازنده با پايان يافتن يك سيكل كلاك بايستي عمليات مقرر را به اتمام رسانده باشد. اگر در اين بازهي زماني بخشي از پردازنده قادر به تكميل عمليات در حال اجرا نباشد، فركانس كلاك براي آن پردازنده بيشتر از ظرفيت آن بوده و تراشه در اين شرايط از كار بازخواهد ايستاد. طراحان اين كندترين بخش تراشه را مسير بحراني (Critical Path) مينامند و اين بخش تعيينكنندهي حداكثر فركانس يك پردازنده است. تجاوز از يك فركانس معين سبب ميشود، ترانزيستورها با سرعت كافي سوئيچ نشوند و اختلال در روند كار يا توليد خروجيهاي نادرست آغاز شود.

فرايند سوئيچ ترانزيستورها را ميتوان با افزايش ولتاژ تغذيه پردازنده تا حد معيني افزايش داد و افزايش بيش از حد ولتاژ خود ممكن است عامل ايجاد اختلال باشد. از سويي، افزايش بيش از حد ولتاژ خطر سوختن پردازنده را در پي دارد. با افزايش هر يك از دو عامل فركانس يا ولتاژِ يك پردازنده گرماي بيشتري توليد ميشود و توان مصرفي افزايش مييابد. علت اين است كه توان پردازنده مستقيماً متناسب با فركانس (سرعت كلاك) و مجذور ولتاژ تغذيه است. براي تعيين توان مصرفي يك پردازنده، معمولاً هر ترانزيستور را به مثابهي يك خازن كوچك تصور ميكنيم كه هنگام تغيير مقادير، بايد شارژ يا دشارژ شود.

تحويل توان پايدار به پردازنده گاه آنقدر مهم است كه نيمي از پينهاي فيزيكي روي تراشه، تنها براي تأمين توان مصرفي مورد استفاده قرار ميگيرد يا نقش اتصال زمين را ايفا ميكند. بعضي تراشهها ممكن است حين بارگذاري كامل بيش از ۱۵۰ آمپر جريان بكشند و هر ميليآمپر از اين جريان بايد با دقت و ظرافت زيادي مديريت شود. در بيان حساسيت حجم توان مصرفي تراشه همين بس كه هر پردازنده در واحد سطح ميزان گرمايي بيشتر از يك راكتور هستهاي توليد ميكند.

سيگنال كلاك در پردازندههاي مدرن رقمي در حدود ۳۰ تا ۴۰ درصد مجموع توان مصرفي تراشه را به خود اختصاص ميدهد؛ چرا كه اين توليد و حفظ و بهرهبرداري از اين سيگنال بسيار پيچيده است و بايد بخشهاي مختلف زيادي را به كار اندازد. براي صرفهجويي در مصرف انرژي، در طراحيهايي با بهرهوري بالا اجزايي از تراشه كه در حال استفاده نيست، خاموش ميشود. اين كار با خاموشكردن سيگنال كلاسيك در ورودي آن جزء (Signal Gating) يا قطع دسترسي به توان (Power Gating) عملياتي ميشود.

سيگنال كلاك چالش ديگري در طراحي پردازنده نيز به بار ميآورد. با افزايش مداوم فركانس كلاك پردازندهها، موانع ناشي از قوانين فيزيك بيشتر ميشود. اگر ميتوانستيم سيگنال كلاك را به يك سر تراشه متصل كنيم، در آن واحد سيگنال از سمت ديگر خارج ميشد و فرصتي براي همگامسازي اجزا پديد نميآمد. براي همگامسازي تمام اجزاي تراشه، سيگنال كلاك با استفاده از ساختاري به نام H-Tree در سراسر تراشه توزيع ميشود. اين ساختار تضمين ميكند كه تمامي نقاط انتهايي، فاصلهي يكساني از مركز داشته باشند.

ساختار H-Tree براي حفظ و توزيع سيگنال كلاك در سطح پردازنده

شايد طراحي تك به تك ترانزيستورها، سيگنال كلاك و اتصال توان در يك تراشه كاري بسيار پيچيده و ملال آور به انديشه متخصصين برسد و در حقيقت هم همينطور است. شركتهايي مثل اينتل، كوالكام و AMD هزاران مهندس طراح تراشه دارند، اما حتي براي آنها هم طراحي تمامي جنبههاي عملي يك تراشه ناممكن است. اين شركتها براي طراحي پردازندههاي خود با آن گستردگي عظيم، از ابزارهاي مختلف پيچيدهاي استفاده ميكنند تا طراحيها و شماتيكهاي مدار مورد انديشه متخصصين را براي آنها خلق كنند. اين ابزارها شرح سطح بالايي از آنچه كه هر يك از اجزاي تراشه بايد انجام دهد دريافت ميكنند و در نهايت بهينهترين پيكربندي سختافزاري را براي برآوردهكردن الزامات و سطح عملكرد مورد انديشه متخصصين به دست ميدهند. تراشهسازان به سمت تكنيك جديدي به نام High Level Synthesis گرايش يافتهاند. اين تكنيك به توسعهدهندگان اجازه خواهد داد تا سطح عملكرد مورد انديشه متخصصين خود را در قالب كدهايي بيان كنند و سپس كامپيوترها نحوهي دستيابي بهينه به سختافزار مورد انديشه متخصصين را ميسنجند و در اختيار مهندسان قرار ميدهند.

تراشهسازان تلاش ميكنند عيوب تراشه را در مرحله مطالعه و اعتبارسنجي طراحيها، پيش از رسيدن به خط توليد برطرف كنند؛ اگر عيوب به تراشه فيزيكي منتقل شود، ديگر قابل رفع نيستند

درست همانطور كه برنامهنويسان برنامههاي كامپيوتري را از طريق كدها تعريف ميكنند، طراحان هم ميتوانند سختافزار را از طريق كد تعريف و شناسايي كنند. زبانهاي برنامهنويسي بهمانند Verilog و VHDL توسعه يافته است كه به طراحان سختافزار اجازه ميدهد، سطوح عملكرد مدارهاي منطقي در حال ساخت را به زباني قابل فهم براي ماشين بيان كنند. در مرحلهي بعد شبيهسازي، مطالعه و اعتبارسنجي اين طراحيها انجام ميپذيرد و اگر همهچيز مورد تأييد باشد، امكان سنتز و همگذاري ترانزيستورهاي خاص براي ساختن مدارات مورد انديشه متخصصين فراهم ميشود. روند مطالعه و اعتبارسنجي شايد به اندازهي طراحي يك هسته يا قطعهي كش جديد درخور توجه به انديشه متخصصين نرسد، اما به لحاظ منطقي از اهميت بيشتري برخوردار است. به ازاي هر مهندس طراحي كه يك شركت استخدام ميكند، ممكن است پنج مهندس مطالعهگر يا حتي بيشتر از آن استخدام شود.

مطالعه و اعتبارسنجي يك طراحي جديد معمولاً زمان و هزينهي بيشتري در مقايسه با ساخت تراشهي فيزيكي واقعي ميبرد. شركتها زمان و پول زيادي را صرف مطالعه و اعتبارسنجي طراحيها ميكنند؛ چرا كه به مجرد آنكه تراشهاي به مرحله توليد رسيد، ديگر فرصتي براي رفع عيوب احتمالي آن وجود ندارد. ايرادهاي نرمافزاري با انتشار وصلهها قابل رفع است، اما براي رفع ايرادهاي سختافزاري غالباً راهكاري وجود ندارد. براي مثال اينتل در واحد تقسيم اعشاري برخي از پردازندههاي پنتيوم خود باگي دارد كه تا به امروز دو ميليارد دلار هزينه روي دستشان گذاشته است.

از انديشه متخصصيناتي فراتر، تصور ساخت يك تراشهي بسيار پيچيده با ميلياردها ترانزيستور و آنچه كه همه آنها در كنار هم انجام ميدهند، بسيار سخت جلوه ميكند. با وجود اين اگر براساس دانستههايي كه از اين مقاله به دست آورديم، هر پردازنده را مجموعهاي از اجزاي سادهتر تصور كنيم كه هر يك وظيفهاي با پيچيدگي كمتر را انجام ميدهد، حل مسئله آسانتر ميشود. ترانزيستورها گيتهاي منطقي را ميسازند، تركيبي از گيتهاي منطقي باعث تشكيل واحدهاي عملياتي ميشود كه هر يك وظيفهي خاصي را اجرا ميكنند و در نهايت اين واحدهاي عملياتي به يكديگر ميپيوندند تا معماريهاي دستورالعملي را كه در اين مقاله در مورد آنها صحبت كرديم، پيادهسازي كنند.

در قسمت دوم مقاله در مورد روشهاي ساخت فيزيكي تراشههاي پردازنده و فناوريهاي ساخت آنها صحبت خواهيم كرد و با خطمشيهاي كنوني و آيندهي توسعهي معماريهاي كامپيوتري آشنا خواهيم شد.

مشخصات متخصص كامل، ارزش پردازنده در فروشگاههاي اينترنتي و مقايسهي كامل انواع CPU را در بخش محصولات مشاهده كنيد؛انواع CPU اينتل از جمله سري Core i3، Core i5 و Core i7 و پردازندههاي مركزي AMD رايزن (Ryzen) براي مقايسه و خريد در دسترس متخصصان است.

هم انديشي ها