معماري ARM چيست؟ چه تفاوتي با x86 اينتل دارد؟

امروزه هر جا صحبت از تلفن هوشمند يا تبلت به ميان ميآيد، حتما نام ARM نيز به گوش ميرسد. پردازنده اكثر تبلت و تلفنهاي هوشمند بازار مبتني بر معماري ARM است. اما ARM به چه معناست؟ معماري ARM چيست؟ چه تفاوتي با x86 اينتل ميكند؟ چرا اين معماري تا به اين اندازه محبوب شده و دنياي موبايل را تحت كنترل خود قرار داده است؟ در ادامه مطلب براي رسيدن به پاسخ اين پرسشها با اخبار تخصصي، علمي، تكنولوژيكي، فناوري مرجع متخصصين ايران همراه باشيد.

در اين مقاله به معرفي ARM، تاريخچه آن و مطالعه كلي نسلهاي مختلف CPUهاي ARM ميپردازيم اما در آينده نسلهاي پردازندههاي ARM را با يكديگر مقايسه نموده و توضيحات كاملي در مورد هر نسل ارائه خواهيم كرد.

تاريخچه ARM

ARM نوعي از معماري پردازندههاي كامپيوتري است كه بر طبق طراحي RISC CPU و توسط كمپاني بريتانيايي ARM Holding طراحي شده است. معماري ARM كه دستورالعملهاي 32 بيتي را پردازش ميكند از دهه 1980 تا به امروز در حال توسعه است.

ARM مخفف Advanced RISC Machine است و از آنجايي كه اين معماري براساس طراحي RISC بنا شده، هسته اصلي CPU نياز به 35 هزار ترانزيستور دارد اين در حالي است كه پردازندههاي معمولي رايج x86 كه براساس CISC طراحي شدهاند حداقل نياز به ميليونها ترانزيستور دارند. مهمترين دليل مصرف بسيار پايين انرژي در پردازندههاي مبتني بر ARM كه باعث استفاده گسترده آنها در ابزارهاي پرتابل مانند تلفن هوشمند يا تبلت شده نيز همين موضوع است.

جالب است بدانيد كه شركت ARM Holding خود توليدكننده پردازنده نيست و در عوض گواهي استفاده از معماري ARM را به ديگر توليدكنندگان نيمه هادي ميفروشد. كمپانيها نيز به راحتي تراشههاي خود را براساس معماري ARM توليد ميكنند. از جمله كمپانيهايي كه پردازنده خود را براساس معماري ARM طراحي ميكنند ميتوان به اپل در تراشههاي Ax، سامسونگ در پردازندههاي Exynos، انويديا در تگرا و كوالكام در پردازندههاي Snpdragon اشاره كرد.

در سال 2011 مشتريان ARM توانستند 7.9 ميليارد ابزار مبتني بر اين معماري را وارد بازار كنند. شايد تصور ميكنيد كه پردازندههاي مبتني بر ARM تنها در تبلت و تلفنهاي هوشمند بكار گرفته ميشوند، اما جالب است بدانيد كه در همين سال بيش از 95 درصد تلفنهاي هوشمند دنيا، 90 درصد ديسكهاي سخت (HDD)، حدود 40 درصد تلويزيونهاي ديجيتال و ستتاپباكسها، 15 درصد ميكروكنترلرها و 20 درصد كامپيوترهاي موبايل مجهز به پردازندههاي مبتني بر معماري ARM بودهاند. بدون شك اين آمار در سال 2012 رشد فوقالعاده چشم گيري را تجربه كرده است، چون بازار تلفنهاي هوشمند و تبلتهاي در سال جاري پيشرفت قابل ملاحظهاي داشتهاند.

تا اينجاي كار معماري ARM تنها برروي پلتفرم 32 بيتي با عرض حافظه 1 بايت كار ميكرد. اما با معرفي ARMv8 اين معماري همراهي از دستورات 64 بيتي را نيز آغاز كرد كه البته هنوز در سيستم-روي-يك-چيپها بكار گرفته نشده است. در سال 2012 مايكروسافت نيز نسخه ويندوز سازگار با معماري ARM را به همراه تبلت سرفيس RT معرفي كرد. AMD نيز اعلام نموده كه قصد دارد در سال 2014 سرورهاي مبتني بر معماري 64 بيتي ARM را روانه بازار كند.

همانطور كه پيشتر اشاره كرديم، ARM گواهي استفاده از معماري خود را به شركتهاي ديگر ميدهد، كمپانيهايي كه در حال حاضر گواهي استفاده از ARM را دارند عبارتند از: AMD, آلكاتل, اپل, AppliedMicro, Atmel, Broadcom, Cirrus Logic, CSR plc, Digital Equipment Corporation, Ember, Energy Micro, Freescale, فوجيتسو, Fuzhou Rockchip, هواوي, اينتل توسط شركتهاي زير شاخه, ال جي, Marvell Technology Group, Microsemi, مايكروسافت, NEC, نينتندو, Nuvoton, انويديا, NXP (formerly Philips Semiconductor), Oki, ON Semiconductor, پاناسونيك, كوالكام, Renesas, Research In Motion, سامسونگ, شارپ, Silicon Labs, سوني, اريكسون, STMicroelectronics, Symbios Logic, Texas Instruments, توشيبا, ياماها و ZiiLABS

RISC و CISC يا ARM در مقابل x86

RISC كه مخفف Reduced instruction Set Computing يا مجموعه دستورات ساده شده است در واقع نوعي از طراحي CPU است كه پايه و اساس آن، ساده سازي دستورات است كه منجر به بازده بالا و سرعت بخشيدن به اجراي دستورات ميشود. پردازدهاي كه براساس اين طراحي ساخته ميشود را RISC (بخوانيد ريسك) مينامند. مهمترين و معروفترين معماري كه براساس RISC طراحي شده، ARM است. درست نقطه مقابل ريسك، طراحي ديگري با نام CISC وجود دارد كه مخفف Complex Instruction Set Computing يا مجموعه دستورات پيچيده است كه معماري x86 اينتل براساس آن طراحي شده و پردازنده كامپيوترهاي روميزي و لپ تاپها و بسياري از ابزارهاي ديگر از آن بهره ميبرند.

ايده اصلي RISC اولين بار توسط جان كوكي از IBM و در سال 1974 شكل گرفت، انديشه متخصصينيه او به اين موضوع اشاره داشت كه يك كامپيوتر تنها از 20 درصد از دستورات نياز دارد و 80 درصد ديگر، دستورات غيرضروري هستند. پردازندههاي ساخته شده براساس اين طراحي از دستورات كمي همراهي ميكنند به اين ترتيب به ترانزيستور كمتري نيز نياز دارند و ساخت آنها نيز كم هزينه است. با كاهش تعداد ترانزيستورها و اجراي دستورات كمتر، پردازنده در زمان كمتري دستورات را پردازش ميكند. كمي بعد اصطلاح RISC توسط يك استاد دانشگاه كاليفورنيا به نام ديويد پترسون ايجاد شد.

هر دو طراحي RISC و CISC به مراتب در انواع و اقسام ابزارها بكار گرفته ميشوند، اما مفهوم كلي RISC در واقع سيستمي است كه در آن به پردازش دستورات كوچك و به شدت بهينه شده پرداخته ميشود، درست برخلاف CISC كه در آن دستورات پيچيده ارسال ميشوند. يكي از تفاوتهاي عمده بين RISC و CISC نيز در نحوه دسترسي به حافظه و ذخيره و اجراي اطلاعات برروي آن است. در ريسك دسترسي به حافظه تنها از طريق دستورالعملهاي خاصلي قابل انجام است و به عنوان مثال نميتوان از بخشي از دستور add به حافظه دسترسي داشت.

علاوه بر ARM شركتهاي بسيار ديگري از جمله Intel i860, AMD 29k, ARC و غيره از طراحي RISC براي ساخت پردازنده استفاده ميكنند، اما به لطف گسترش تلفن و تبلتها، معماري ARM به عنوان برجستهترين معماري مبتني بر RISC شناخته ميشود.

CISC

در سيسك اوضاع دقيقا برعكس ريسك است و پردازنده قادر به پردازش دستورات پيچيده است به همين دليل نياز به تعداد بيشتر ترانزيستور و همچنين طراحي پيچيدهتر و پردازندههاي گران ارزشتر دارد. ايده اصلي پشت اين طراحي اين است كه برنامه نويسان سادهتر بتوانند نرم افزارهاي خود را توليد كنند و دستورات را سادهتر به CPU ارجاع دهند. به لطف همراهي اينتل و توليدكنندگان نرم افزار، CISC به شدت محبوب شد و تمام كامپيوترها از پردازنده مبتني بر اين طراحي بهره بردند.

برخي تصور ميكنند كه ريسك قادر به اجراي دستورات زياد نيست اما در حقيقت ريسك به اندازه سيسك ميتواند دستورات مختلف را اجرا كند اما مهمترين تفاوت اين دو در اين است كه در RISC تمام دستورات با يك فرمت، دقيقا يك فرمت صادر ميشوند و پردازش تمام دستورات يك زمان مشخص طول ميكشد، معمولا در ريسك در هر سيكل، پردازنده يك دستور را اجرا ميكند.

اما در CISC مجموعهاي از دستورات بصورت فشرده و با آدرس دهي مختلف به يكباره پردازش ميشوند، مثل اعداد اعشاري يا تقسيم كه در طراحي RISC وجود ندارند. از آنجايي كه دستورات در RISC سادهتر هستند پس سريعتر اجرا ميشوند و نياز به ترانزيستور كمتري دارند، ترانزيستور كمتر هم به معني دماي كمتر، مصرف پايينتر و فضاي كمتر است كه آن را براي ابزارهاي موبايل مناسب ميكند.

معماري پردازندههاي مبتني بر طراحي RISC طي سالهاي گذشته پيشرفت چشمگيري داشته و اجراي دستورات پيچيده را نيز ميسر كرده است و توليدكنندگان نرم افزاري نيز به سمت ساخت نرمافزارهاي مبتني بر اين معماري گرايش پيدا كردهاند. لازم است بدانيد كه كامپيوترهاي اوليه مك نيز از پردازنده مبتني بر RISC بهره ميبردند.

اما در واقع پردازندههاي CISC بسيار سريعتر و پرقدرتتر از RISCها هستند و قادر به پردازش امور سنگين ميباشند اما در عوض گرانارزشتر، پرمصرفتر بوده و دماي بيشتري نيز توليد ميكنند. در CISC تمركز برروي سختافزار است و در RISC برروي نرمافزار، در CISC دستورات بصورت پيچيده به پردازنده ارسال ميشوند ولي در RISC نرمافزار دستورات را ساده كرده و به عنوان مثال يك عمليات پيچيده را در قالب چندين دستور ساده به پردازنده ارسال ميكند و پردازنده دستورات ساده را به سرعت پردازش نموده و نتيجه را باز ميگرداند. پس كدهاي نرمافزارهاي سازگار با RISC طولاني تر ولي كدهاي مربوط به نرمافزارهاي CISC كوتاهتر و پيچيدهتر هستند. البته اين بدين معنا نيست كه مثلا اگر قرار است براي اندرويد يا iOS برنامه بنويسيد بايد چند هزار خط بيشتر از معادل كامپيوتر ويندوزي آن كد نويسي كنيد، در واقع كامپايلرها كدها را به دستورات كوچك زياد تبديل ميكنند و برنامه نويس به سختي متوجه نوع پردازش دستورات ميشود.

اگر بخواهيم در مورد اين دو طراحي صحبت كنيم مباحثه پيچيده و كسل كننده خواهد شد پس به همين جا بسنده ميكنيم اما اگر تمايل داريد تا در مورد اين طراحيها بيشتر بدانيد به اين دو لينك مراجعه كنيد: CISC و RISC

سيستم-روي-يك-چيپها و معماري ARM

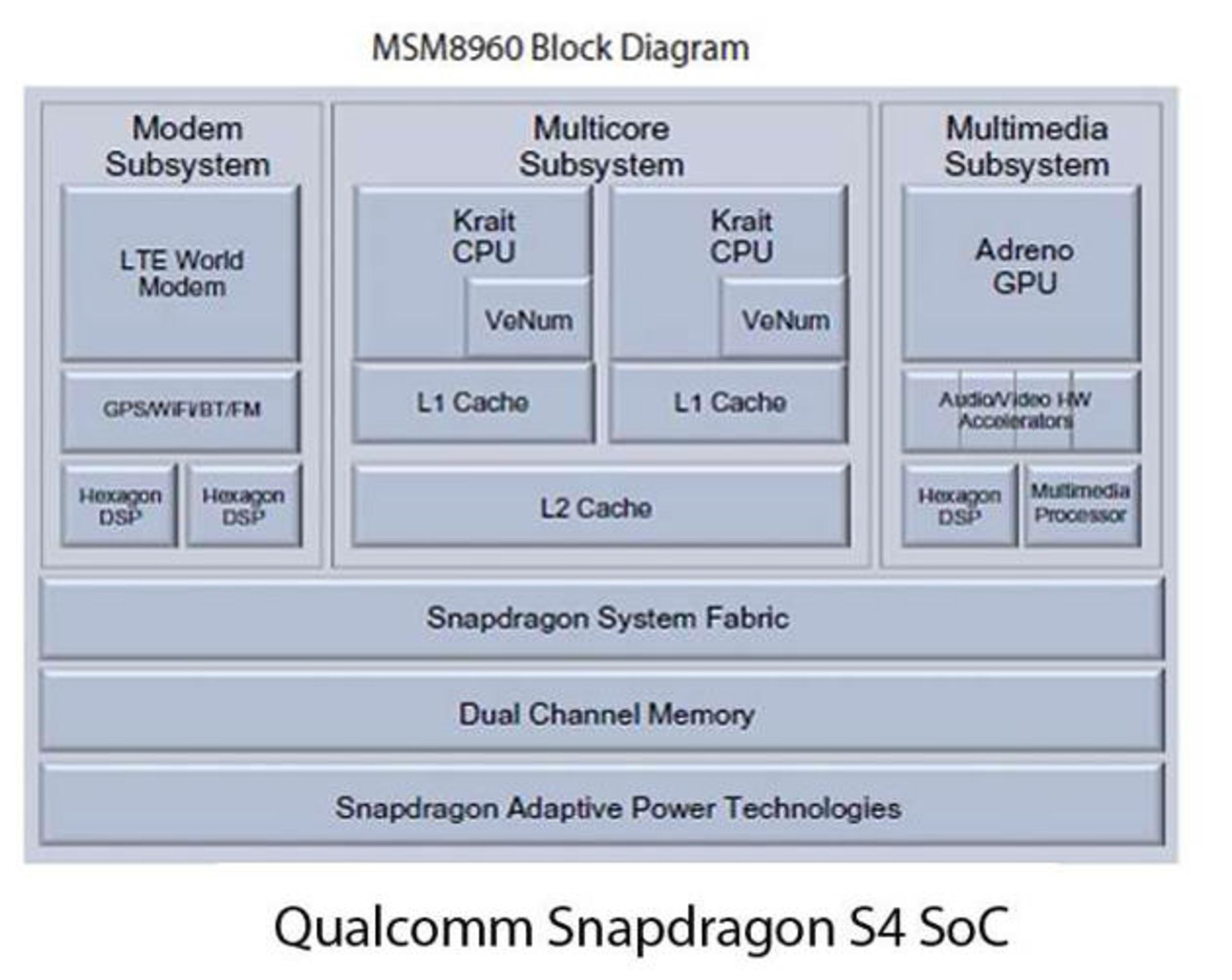

چندين نوع مختلف از معماري براي پردازندههاي ARM وجود دارد كه از آن جمله ميتوان به ARM V2 ،ARMv3 Arm v7 و ...اشاره كرد. كمپانيها براي استفاده از هر كدام از اين طراحيها بايد گواهي مربوط به آن را از ARM Holder دريافت كنند. كمپانيها از اين معماري در ساخت پردازنده هاي مورد انديشه متخصصين خود بهره برده و در نهايت يا يكپارچه سازي آن با واحد پردازش گرفيك (GPU)، حافظه رم و قسمت كنترلر باند راديويي (در تلفنهاي هوشمند) سيستم -روي-يك-چيپ خود را مي سازند .

سيستم-روي-يك-چيپ (System on a Chip) كه آن را به اختصار SoC مينامند در واقع يك تراشه است كه در آن پردازنده اصلي (CPU)، پردازنده گرافيك (GPU)، حافظه رم، كنترلرهاي ورودي و خروجي و بعضا كنترلر باند راديويي قرار دارند. پس لازم است بدانيد كه كل SoC براساس معماري ARM توليد نميشود و تنها بخش CPU آن بر مبناي معماري ARM طراحي و توليد ميگردد. پس اين باور كه فلان SoC براساس معماري ARM ساخته شده، اشتباه است و بخش پردازنده اصلي اكثر SoCها براساس يكي از طراحهاي معماري ARM ساخته ميشوند.

از جمله سيستم-روي-يك-چيپهايي كه هسته اصلي آنها براساس معماري ARM طراحي شدهاند ميتوان به 3 نسل اول تگرا انويديا، Quatro شركت CSRT، نوا شركت اريكسون، OMAP شركت تكزاس، Exynos شركت سامسونگ و Ax شركت اپل اشاره كرد. اين شركت ها از معماري ARM و همچنين معماري يكي از هستههاي طراحي شده توسط اين شركت بهره بردهاند.

اما شركتها ميتوانند گواهي استفاده از معماري ARM را تهيه كرده و سپس بر اساس آن هسته سفارشي مورد انديشه متخصصينشان را طراحي كنند يعني به جاي اينكه هسته CPU را براساس Cortex-A9 يا Cortex-A15 يا ديگر هستههاي ARM بسازنند، خودشان براساس معماري يكي از خانوادههاي ARM، هسته خاص خود را طراحي كنند. به عنوان مثال سيستم-روي-يك-چيپ A6 اپل، X-Gene ،Krait كوالكام، StrongARM شركت DEC ،XScale شركت Marvell اينتل يا Project Denver شركت انويديا اينگونه هستند و اگر چه بخش CPU از سيستم-روي-يك-چيپ آنها براساس معماري ARM طراحي شدهاند، اما طراحي هستهها با آنچه ARM پيشنهاد كرده متفاوت هستند.

انواع مختلف هستههاي مبتني بر ARM

همانطور كه پيشتر اشاره كرديم، شركت ARM Holding خود نسبت به طراحي هسته براساس معماري ARM اقدام ميكند و هستههاي متفاوتي را براساس نسلهاي مختلف اين معماري عرضه كرده است، جديدترين معماري اين شركت ARM v8 است كه از دستورات 64 بيتي همراهي ميكند و دو هسته Cortex A53 و Cortex A57 نيز براساس همين معماري طراحي و پيشنهاد شدهاند. انتظار ميرودي SoCهاي سال آينده از اين معماري بهره مند شوند، در جدول زير كل هستههاي طراحي شده توسط ARMرا مشاهده خواهيد كرد:

ARM Family | ARM Architecture | ARM Core | Feature | Cache (I/D), MMU | Typical MIPS @ MHz |

|---|---|---|---|---|---|

ARM1 | ARMv1 | ARM1 | First implementation | None |

|

ARM2 | ARMv2 | ARM2 | ARMv2 added the MUL (multiply) instruction | None | 4 MIPS @ 8 MHz 0.33 DMIPS /MHz |

ARMv2a | ARM250 | Integrated MEMC (MMU), Graphics and IO processor. ARMv2a added the SWP and SWPB (swap) instructions. | None, MEMC1a | 7 MIPS @ 12 MHz | |

ARM3 | ARMv2a | ARM3 | First integrated memory cache. | 4 KB unified | 12 MIPS @ 25 MHz 0.50 DMIPS/MHz |

ARM6 | ARMv3 | ARM60 | ARMv3 first to support 32-bit memory address space (previously 26-bit) | None | 10 MIPS @ 12 MHz |

ARM600 | As ARM60, cache and coprocessor bus (for FPA10 floating-point unit). | 4 KB unified | 28 MIPS @ 33 MHz | ||

ARM610 | As ARM60, cache, no coprocessor bus. | 4 KB unified | 17 MIPS @ 20 MHz 0.65 DMIPS/MHz | ||

ARM7 | ARMv3 | ARM700 |

| 8 KB unified | 40 MHz |

ARM710 | As ARM700, no coprocessor bus. | 8 KB unified | 40 MHz | ||

ARM710a | As ARM710 | 8 KB unified | 40 MHz 0.68 DMIPS/MHz | ||

ARM7TDMI | ARMv4T | ARM7TDMI(-S) | 3-stage pipeline, Thumb | none | 15 MIPS @ 16.8 MHz 63 DMIPS @ 70 MHz |

ARM710T | As ARM7TDMI, cache | 8 KB unified, MMU | 36 MIPS @ 40 MHz | ||

ARM720T | As ARM7TDMI, cache | 8 KB unified, MMU with Fast Context Switch Extension | 60 MIPS @ 59.8 MHz | ||

ARM740T | As ARM7TDMI, cache | MPU |

| ||

ARM7EJ | ARMv5TEJ | ARM7EJ-S | 5-stage pipeline, Thumb, Jazelle DBX, Enhanced DSP instructions | none |

|

ARM8 | ARMv4 | ARM810 [4] [5] | 5-stage pipeline, static branch prediction, double-bandwidth memory | 8 KB unified, MMU | 84 MIPS @ 72 MHz 1.16 DMIPS/MHz |

ARM9TDMI | ARMv4T | ARM9TDMI | 5-stage pipeline, Thumb | none |

|

ARM920T | As ARM9TDMI, cache | 16 KB/16 KB, MMU with FCSE (Fast Context Switch Extension) [6] | 200 MIPS @ 180 MHz | ||

ARM922T | As ARM9TDMI, caches | 8 KB/8 KB, MMU |

| ||

ARM940T | As ARM9TDMI, caches | 4 KB/4 KB, MPU |

| ||

ARM9E | ARMv5TE | ARM946E-S | Thumb, Enhanced DSP instructions, caches | variable, tightly coupled memories, MPU |

|

ARM966E-S | Thumb, Enhanced DSP instructions | no cache, TCMs |

| ||

ARM968E-S | As ARM966E-S | no cache, TCMs |

| ||

ARMv5TEJ | ARM926EJ-S | Thumb, Jazelle DBX, Enhanced DSP instructions | variable, TCMs, MMU | 220 MIPS @ 200 MHz | |

ARMv5TE | ARM996HS | Clockless processor, as ARM966E-S | no caches, TCMs, MPU |

| |

ARM10E | ARMv5TE | ARM1020E | 6-stage pipeline, Thumb, Enhanced DSP instructions, (VFP) | 32 KB/32 KB, MMU |

|

ARM1022E | As ARM1020E | 16 KB/16 KB, MMU |

| ||

ARMv5TEJ | ARM1026EJ-S | Thumb, Jazelle DBX, Enhanced DSP instructions, (VFP) | variable, MMU or MPU |

| |

ARM11 | ARMv6 | ARM1136J(F)-S [7] | 8-stage pipeline, SIMD, Thumb, Jazelle DBX, (VFP), Enhanced DSP instructions | variable, MMU | 740 @ 532–665 MHz (i.MX31 SoC), 400–528 MHz |

ARMv6T2 | ARM1156T2(F)-S | 8-stage pipeline, SIMD, Thumb-2, (VFP), Enhanced DSP instructions | variable, MPU |

| |

ARMv6Z | ARM1176JZ(F)-S | As ARM1136EJ(F)-S | variable, MMU + TrustZone | 965 DMIPS @ 772 MHz, up to 2 600 DMIPS with four processors [8] | |

ARMv6K | ARM11 MPCore | As ARM1136EJ(F)-S, 1–4 core SMP | variable, MMU |

| |

SecureCore | ARMv6-M | SC000 |

|

| 0.9 DMIPS/MHz |

ARMv4T | SC100 |

|

|

| |

ARMv7-M | SC300 |

|

| 1.25 DMIPS/MHz | |

Cortex-M | ARMv6-M | Cortex-M0 [9] | Microcontroller profile, Thumb + Thumb-2 subset (BL, MRS, MSR, ISB, DSB, DMB), [10] hardware multiply instruction (optional small), optional system timer, optional bit-banding memory | No cache, No TCM, No MPU | 0.84 DMIPS/MHz |

Cortex-M0+ [11] | Microcontroller profile, Thumb + Thumb-2 subset (BL, MRS, MSR, ISB, DSB, DMB), [10] hardware multiply instruction (optional small), optional system timer, optional bit-banding memory | No cache, No TCM, optional MPU with 8 regions | 0.93 DMIPS/MHz | ||

Cortex-M1 [12] | Microcontroller profile, Thumb + Thumb-2 subset (BL, MRS, MSR, ISB, DSB, DMB), [10] hardware multiply instruction (optional small), OS option adds SVC / banked stack pointer, optional system timer, no bit-banding memory | No cache, 0-1024 KB I-TCM, 0-1024 KB D-TCM, No MPU | 136 DMIPS @ 170 MHz, [13] (0.8 DMIPS/MHz FPGA-dependent) [14] | ||

ARMv7-M | Cortex-M3 [15] | Microcontroller profile, Thumb / Thumb-2, hardware multiply and divide instructions, optional bit-banding memory | No cache, No TCM, optional MPU with 8 regions | 1.25 DMIPS/MHz | |

ARMv7E-M | Cortex-M4 [16] | Microcontroller profile, Thumb / Thumb-2 / DSP / optional FPv4 single-precision FPU, hardware multiply and divide instructions, optional bit-banding memory | No cache, No TCM, optional MPU with 8 regions | 1.25 DMIPS/MHz | |

Cortex-R | ARMv7-R | Cortex-R4 [17] | Real-time profile, Thumb / Thumb-2 / DSP / optional VFPv3 FPU, hardware multiply and optional divide instructions, optional parity & ECC for internal buses / cache / TCM, 8-stage pipeline dual-core running lockstep with fault logic | 0-64 KB / 0-64 KB, 0-2 of 0-8 MB TCM, opt MPU with 8/12 regions |

|

Cortex-R5 (MPCore) [18] | Real-time profile, Thumb / Thumb-2 / DSP / optional VFPv3 FPU and precision, hardware multiply and optional divide instructions, optional parity & ECC for internal buses / cache / TCM, 8-stage pipeline dual-core running lock-step with fault logic / optional as 2 independent cores, low-latency peripheral port (LLPP), accelerator coherency port (ACP) [19] | 0-64 KB / 0-64 KB, 0-2 of 0-8 MB TCM, opt MPU with 12/16 regions |

| ||

Cortex-R7 (MPCore) [20] | Real-time profile, Thumb / Thumb-2 / DSP / optional VFPv3 FPU and precision, hardware multiply and optional divide instructions, optional parity & ECC for internal buses / cache / TCM, 11-stage pipeline dual-core running lock-step with fault logic / out-of-order execution / dynamic register renaming / optional as 2 independent cores, low-latency peripheral port (LLPP), ACP [19] | 0-64 KB / 0-64 KB, ? of 0-128 KB TCM, opt MPU with 16 regions |

| ||

Cortex-A | ARMv7-A | Cortex-A5 [21] | Application profile, ARM / Thumb / Thumb-2 / DSP / SIMD / Optional VFPv4-D16 FPU / Optional NEON / Jazelle RCT and DBX, 1–4 cores / optional MPCore, snoop control unit (SCU), generic interrupt controller (GIC), accelerator coherence port (ACP) | 4-64 KB / 4-64 KB L1, MMU + TrustZone | 1.57 DMIPS / MHz per core |

Cortex-A7 MPCore [22] | Application profile, ARM / Thumb / Thumb-2 / DSP / VFPv4-D16 FPU / NEON / Jazelle RCT and DBX / Hardware virtualization, in-order execution, superscalar, 1–4 SMP cores, Large Physical Address Extensions (LPAE), snoop control unit (SCU), generic interrupt controller (GIC), ACP, architecture and feature set are identical to A15, 8-10 stage pipeline, low-power design [23] | 32 KB / 32 KB L1, 0-4 MB L2, L1 & L2 have Parity & ECC, MMU + TrustZone | 1.9 DMIPS / MHz per core | ||

Cortex-A8 [24] | Application profile, ARM / Thumb / Thumb-2 / VFPv3 FPU / Optional NEON / Jazelle RCT and DAC, 13-stage superscalar pipeline | 16-32 KB / 16-32 KB L1, 0-1 MB L2 opt ECC, MMU + TrustZone | up to 2000 (2.0 DMIPS/MHz in speed from 600 MHz to greater than 1 GHz) | ||

Cortex-A9 MPCore [25] | Application profile, ARM / Thumb / Thumb-2 / DSP / Optional VFPv3 FPU / Optional NEON / Jazelle RCT and DBX, out-of-order speculative issue superscalar, 1–4 SMP cores, snoop control unit (SCU), generic interrupt controller (GIC), accelerator coherence port (ACP) | 16-64 KB / 16-64 KB L1, 0-8 MB L2 opt Parity, MMU + TrustZone | 2.5 DMIPS/MHz per core, 10,000 DMIPS @ 2 GHz on Performance Optimized TSMC 40G (dual core) | ||

Cortex-A15 MPCore [26] | Application profile, ARM / Thumb / Thumb-2 / DSP / VFPv4 FPU / NEON / Jazelle RCT / Hardware virtualization, out-of-order speculative issue superscalar, 1–4 SMP cores, Large Physical Address Extensions (LPAE), snoop control unit (SCU), generic interrupt controller (GIC), ACP, 15-24 stage pipeline [23] | 32 KB / 32 KB L1, 0-4 MB L2, L1 & L2 have Parity & ECC, MMU + TrustZone | At least 3.5 DMIPS/MHz per core (Up to 4.01 DMIPS/MHz depending on implementation). [27] | ||

ARMv8-A | Cortex-A53 [28] | Application profile, AArch32 and AArch64, 1-4 SMP cores, Trustzone, NEON advanced SIMD, VFPv4, hardware virtualization, dual issue, in-order pipeline | 8~64 KB/8~64 KB L1 per core, 128 KB~2 MB L2 shared, 40-bit physical addresses | 2.3 DMIPS/MHz | |

Cortex-A57 [29] | Application profile, AArch32 and AArch64, 1-4 SMP cores, Trustzone, NEON advanced SIMD, VFPv4, hardware virtualization, multi-issue, deeply out-of-order pipeline | 48 KB/32 KB L1 per core, 512 KB~2 MB L2 shared, 44-bit physical addresses | At least 4.1 DMIPS/MHz per core (Up to 4.76 DMIPS/MHz depending on implementation). | ||

ARM Family | ARM Architecture | ARM Core | Feature | Cache (I/D), MMU | Typical MIPS @ MHz |

اما برخي از توليدكنندگان مانند كوالكام، انويديا يا اپل، طراحهاي شركت ARM Holding را قبول ندارند و خود نسبت به طراحي هسته سفارشي بر مبناي معماري ARM اقدام ميكنند. در جدول زير هستههاي طراحي شده توسط شركتهاي ديگر كه البته بر مبناي معماري يكي از خانودههاي ARM هستند را مشاهده ميكنيد:

Family | ARM Architecture | Core | Feature | Cache (I/D), MMU | Typical MIPS @ MHz |

|---|---|---|---|---|---|

StrongARM | ARMv4 | SA-1 | 5-stage pipeline | 16 KB/8–16 KB, MMU | 203–206 MHz 1.0 DMIPS/MHz |

XScale | ARMv5TE | XScale | 7-stage pipeline, Thumb, Enhanced DSP instructions | 32 KB/32 KB, MMU | 133–400 MHz |

Bulverde | Wireless MMX, Wireless SpeedStep added | 32 KB/32 KB, MMU | 312–624 MHz | ||

Monahans | Wireless MMX2 added | 32 KB/32 KB (L1), optional L2 cache up to 512 KB, MMU | up to 1.25 GHz | ||

Snapdragon | ARMv7-A | Scorpion | Used by some members of the Snapdragon S1, S2, and S3 families. 1 or 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv3 FPU / NEON (128-bit wide) | 256 KB L2 per core | 2.1 DMIPS / MHz per core |

Krait | Used by some members of the Snapdragon S4 family. 1, 2, or 4 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU / NEON (128-bit wide) | 4 KB / 4 KB L0, 16 KB / 16 KB L1, 512 KB L2 per core | 3.3 DMIPS / MHz per core | ||

Apple Ax | ARMv7-A | Apple Swift [32] | Custom ARM core used in the Apple A6 and Apple A6X. 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU / NEON | L1: 32 kB instruction + 32 kB data, L2: 1 MB | 3.5 DMIPS / MHz Per Core |

Family | ARM Architecture | Core | Feature | Cache (I/D), MMU | Typical MIPS @ MHz |

ARMv8 و پلتفرم 64 بيتي

در سال 2011 نسل جديد ARMv8 رسما معرفي شد و همراهي از معماري 64 بيتي به آن اضافه گرديد. در ARMv8 دستورات 32 بيتي برروي سيستمعامل 64 بيتي قابل اجرا هستند و در آن سيستمعاملهاي 32 بيتي نيز از طريق مجازي سازي 64 بيتي اجرا ميشوند. شركتهاي AMD, Micro, Brodom, Calxeda, Hisilicon, Samsung و ST Microelectronics گواهي استفاده از معماري ARMv8 را دريافت كردهاند و اعلام نمودهاند SoCهاي مبتني بر اين معماري را توليد خواهند كرد. خود ARM نيز دو طراحي Cortex-A53 و Cortex-A57 را در 30 اكتبر 2012 معرفي كرد كه هر دو مبتني بر معماري ARMv8 هستند.

لينوكس كه هسته اندرويد نيز است به تازگي هسته اصلي سيستمعامل (Kernel) خود را بروز كرده تا از ARMv8 همراهي كند. انتظار ميرود در سال 2013 بسياري از سيستم-روي-يك-چيپهاي دنيا از معماري ARMv8 بهره ببرند.

چه سيستمعاملهايي از ARM همراهي ميكنند؟

سيستمهاي Acorn: اولين كامپيوتر مبتني بر معماري ARM، كامپيوتر شخصي Acorn بود كه از سيستمعاملي به نام Arthur بهره ميبرد. سيستمعاملي مبتني بر RISC OS كه از معماري ARM پشتياني ميكرد و Acorn و برخي ديگر از توليدكنندگان از آن استفاده ميكردند.

سيستمعاملهاي توكار: معماري ARM از طيف وسيعي از سيستمعاملهاي توكار مانند Windows CE, Windows RT, Symbian, ChibiOS/RT, FreeRTOS, eCos, Integrity, Nucleus PLUS, MicroC/OS-II, QNX, RTEMS, CoOS, BRTOS, RTXC Quadros, ThreadX, Unison Operating System, uTasker, VxWorks, MQX و OSE همراهي ميكند.

يونيكس: يونيكس و برخي از سيستمعاملهاي مبتني بر يونيكس مانند: Inferno, Plan 9, QNX و Solaris از ARM همراهي ميكنند.

لينوكس: بسياري از توزيعهاي لينوكس از ARM همراهي ميكنند از آن جمله ميتوان به اندرويد و كروم گوگل، Arch Linux، بادا سامسونگ، Debian، Fedora،OpenSuse، Ubuntu و WebOS اشاره كرد.

BSD: برخي از مشتقات BSD مانند OpenBSD و iOS و OS X اپل نيز از ARM همراهي ميكند.

ويندوز: معماريهاي ARMv 5, 6 و 7 از ويندوز CE كه در ابزارهاي صنعتي و PDAها استفاده ميشود، همراهي ميكند. ويندوز RT و ويندوز فون نيز از معماري ARMv7 همراهي ميكنند.

گواهي و هزينه استفاده از معماري ARM

ARM خود توليدكننده نيمه هادي نيست و در عوض از راه صدور مجوز استفاده از طراحيهاي خود، درآمد كسب ميكند. گواهي استفاده از معماري ARM شرايط خاص و متنوعي را دارد و در شرايط مختلف هزينه مربوط به استفاده از آن نيز تفاوت ميكند. ARM به همراه گواهينامه خود اطلاعات جامعي در مورد نحوه يكپارچگي قسمتهاي مختلف با هستهها را ارائه ميكند تا توليدكنندگان به راحتي بتوانند از اين معماري در سيستم-روي-يك-چيپهاي خود بهره ببرند.

ARM در سال 2006 و در گزارش سالانه خود اعلام كرد كه 164.1 ميليون دلار از بابت حق امتياز يا حق اختراع، درآمد داشته كه اين مبلغ از بابت فروش گواهي استفاده از معماري اين شركت در 2.45 ميليارد دستگاه مبتني بر ARM بدست آمده است. اين يعني ARM Holding بابت هر گواهي 0.067 دلار درآمد كسب نموده، اما اين رقم ميانگين است و براساس نسلهاي مختلف و نوع هستهها متفاوت خواهد بود. مثلا هستههاي قديمي ارزانتر و معماري جديد گرانتر است.

اما در سال 2006 اين شركت از بابت گواهي استفاده از طراحي هسته پردازنده، نزديك به 119.5 ميليون دلار درآمد بدست آورده است. در آن سال 65 پردازنده براساس معماري هسته هاي ARM ساخته شده بودند كه به اين ترتيب بابت هر گواهي پردازنده مبلغ 1.84 ميليون دلار درآمد كسب كرده است. اين عدد نيز بصورت ميانگين ميباشد و براساس نوع و نسل هستهها متفاوت خواهد بود.

در واقع شركت ARM Holding از معماري ARM دو نوع درآمد دارد يكي بابت استفاده از معماري اين شركت در ابزارهاي مختلف كه بابت هر تلفن يا تبلت يا هر ابزار ديگري مبلغي بدست ميآورد و ديگري بابت هر پردازنده مبتني بر معماري هستههاي ARM نيز يك رقم نسبتا سنگين حدود 2 ميليون دلار دريافت ميكند. در سال 2006 نزديك به 60 درصد درآمد ARM از بابت حق امتياز و 40 درصد بابت گواهي ساخت پردازنده براساس معماري ARM بوده است.

هم انديشي ها